# Taktsynchronisierung und Zeitmessung in einem verteilten Datenerfassungssystem

SEI-Tagung am HZG, 12.03.2014

P. Födisch, J. Sandmann, B. Lange, P. Kaever

Helmholtz-Zentrum Dresden-Rossendorf

# MotivationAnwendung

- Detektorsystem f

ür medizinische Anwendung

- Klinischer Einsatz erfordert off-the-shelf Komponenten

- Bildgebendes Verfahren erfordert Zeitstempel für alle Ereignisse im verteilten System (Genauigkeit <= 1ns)</li>

- Synchronisierung der Detektormodule!

#### 2. Motivation

## Dedizierte Taktverteilung vs. Synchrones Ethernet

|    |    |    | 4   |

|----|----|----|-----|

| l) | Ad | 17 | rte |

|    | CU |    |     |

Taktverteilung SyncE

Installationsaufwand Pegelwandler, Kabel Datenport

- Skalierbarkeit Fanout, Buffer PortanzahlSwitch/Master

- Frequenzstabilität (Jitter) Masteroszillator (<1ps) < 50ps

Synchronisierung

Zeitstempel nicht möglich ohne Protokollbasiert

2. Phasenlage Datenlink

Absolutes Timing mit dedizierter Taktverteilung nicht möglich!

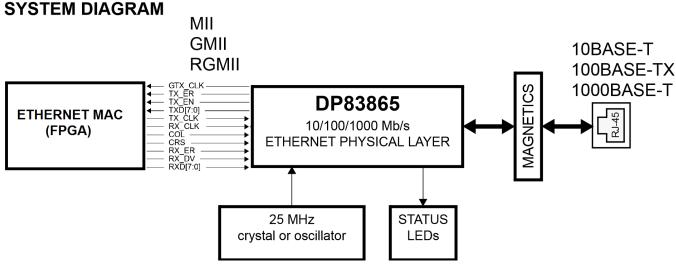

# SystemaufbauGigabit Ethernet Interface

- 2x Texas Instruments

Gig PHYTER DP83865

- FMC LPC Steckverbinder

- Xilinx Spartan 6 FPGA

DRESDEN Concept

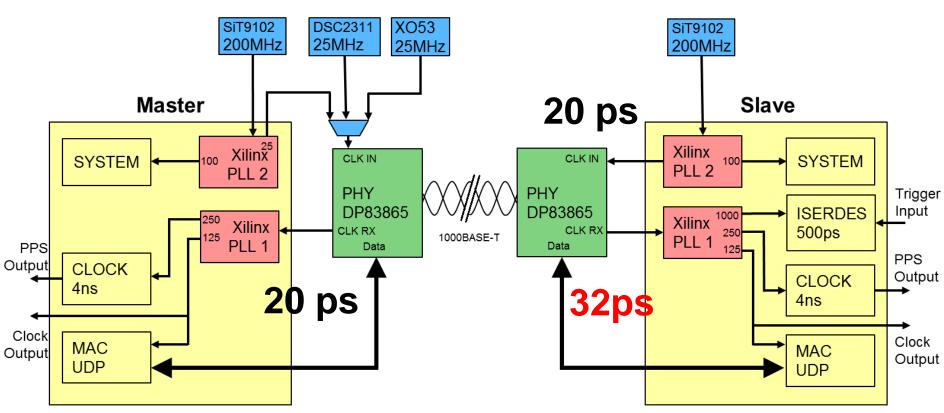

# SystemaufbauGigabit Ethernet

- 1000Base-T erfordert Konfiguration der Link-Partner (Auto-Negotiation)

- 1 Master und 1 Slave (manuelle Konfiguration)

- Master sendet Daten mit lokalem Takt

- Slave sendet Daten mit dem Takt des Masters (Clock Recovery)

- ADC Subsystem on Chip

- "high precision and low jitter Clock Recovery Module" [1]

- 25MHz Mastertakt -> 125MHz Slavetakt (RX\_CLK)

# 2. Systemaufbau Messaufbau

#

**SLAVE**

-GigaPhy

-Spartan6

-onBoard Quarz

#### **MASTER**

-GigaPhy

-Kintex 7

-ext.

**Taktquelle**

# 3. Taktsynchronisierung

## **Ergebnis**

$$TJ = 5 ps$$

43ps

## 3. Taktsynchronisierung

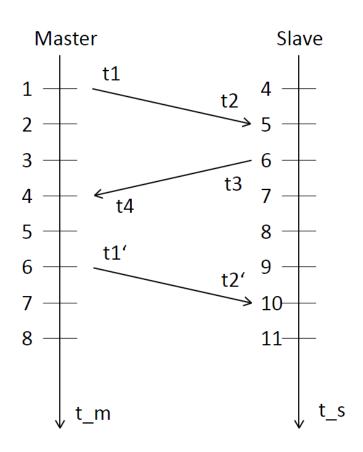

#### **Precision Time Protocol**

Ziel: Synchronisierung von zwei Uhren (Timestamp) mit unterschiedlichen Taktsignalen (Clock)

$$t_m = t_s - offset$$

Berechnung des Offset mit PTP:

$$o = ((t2-t1) - (t4-t3)) * 0.5$$

# 3. Taktsynchronisierung Uhrenabgleich / Pulse Per Second

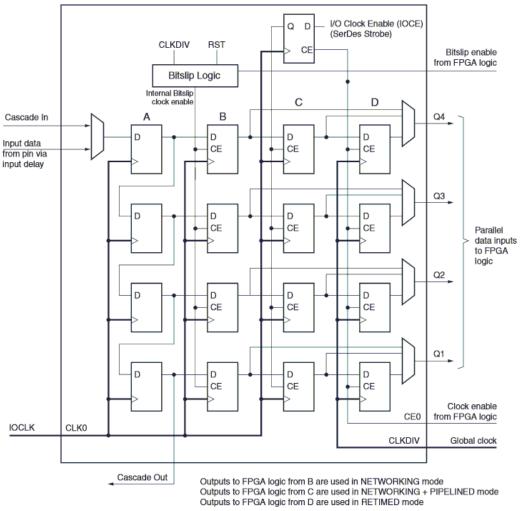

# 4. Zeitmessung Xilinx ISERDES Logic

1:4 Deserializer up to 1050 Mb/s

UG381\_c3\_01\_012413

Figure 3-1: Overview of the ISERDES2 Block in SDR Mode

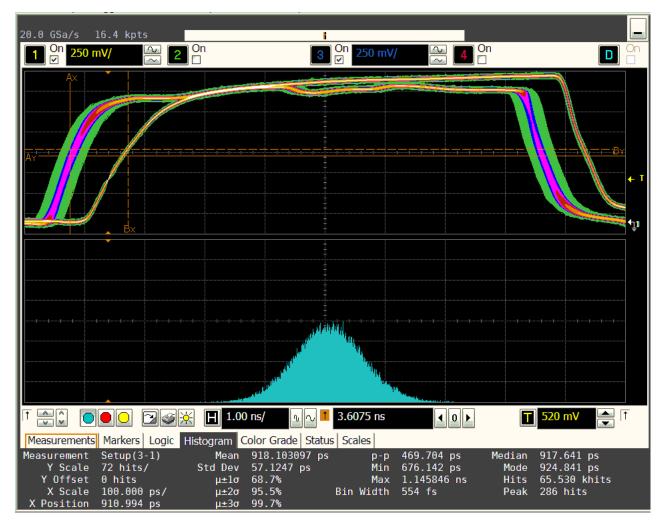

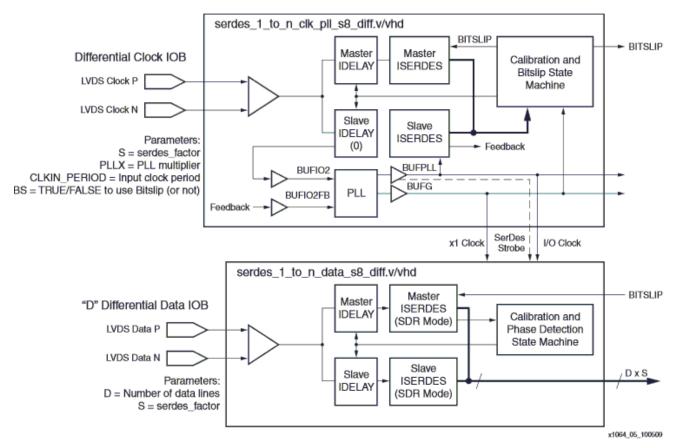

# 4. Zeitmessung

# TDC mit Xilinx ISERDES Logic

Figure 5: Data Reception Using PLL and BUFPLL

Master Serdes:

1 GHz

Slave Serdes:

1 GHz (invertiert)

Sampling Freq: 2GHz 500ps bin width

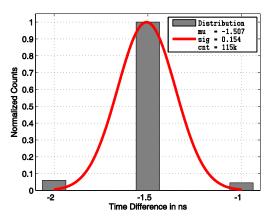

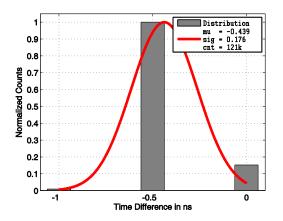

# 4. Zeitmessung

## TDC mit Xilinx ISERDES Logic

#### Timestamp Differenz

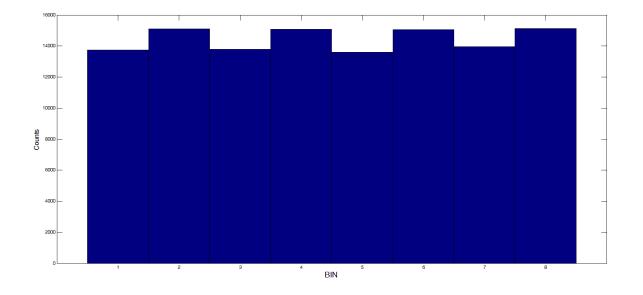

## **TDC BIN Verteilung**

## Vielen Dank für Ihre Aufmerksamkeit