DRD 7.6B MEETING KARLSRUHE 2025

# LOW-MATERIAL PIXEL MODULES: **ALL-SILICON AND THIN HYBRID MODULES**

Y. Dieter<sup>B</sup>, J. Dingfelder<sup>B</sup>, I.-M. Gregor<sup>B,De</sup>, T. Fritzsch<sup>I</sup>, F. Hügging<sup>B</sup>,

K. Kröninger<sup>Do</sup>, H. Krüger<sup>B</sup>, M. Mucha<sup>B</sup>, A. Ulm<sup>B</sup>, J. Vicsher<sup>Do</sup>, M. Vogt<sup>B</sup>,

J. Weingarten<sup>Do</sup>, S. Zhang<sup>B</sup>

<sup>&</sup>lt;sup>B</sup> University of Bonn

De DESY

Do TU Dortmund

Fraunhofer IZM Berlin

# **MOTIVATION**

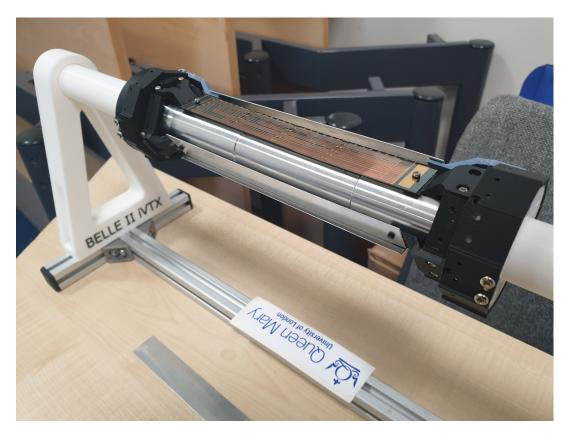

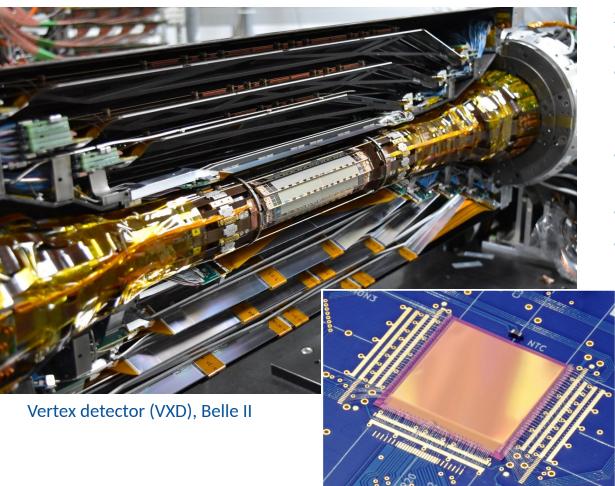

Super low material budget applications e.g. in Belle II:

- Monolithic active CMOS pixel sensor OBELIX, evolving from TJ-Monopix2

- L1+L2: self-supporting, air cooled or contact cooled

- L3-L5: CF structure, water cooled

- Low material budged:

0.2% X<sub>0</sub> (L1+L2) ... 0.8% X<sub>0</sub>

CMOS sensor TJ-Monopix2

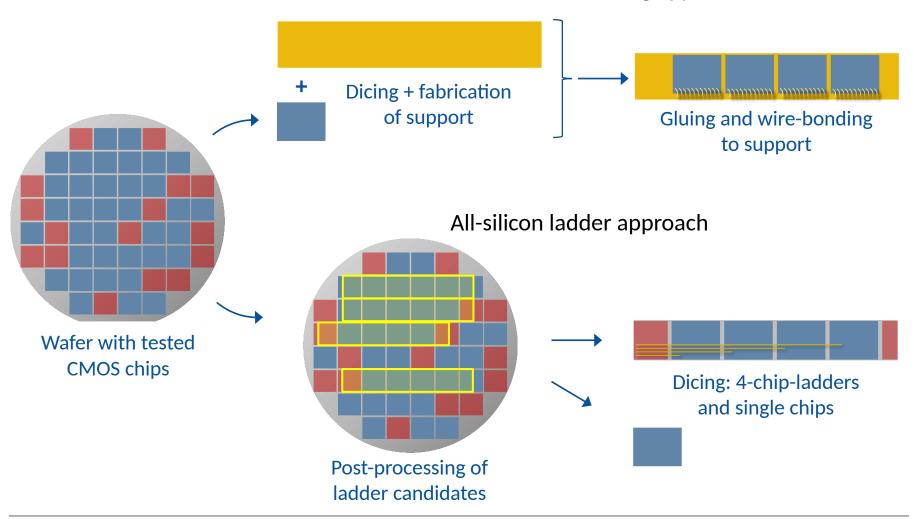

## **ALL-SILICON LADDER CONCEPT**

# Common module-building approach

## **ALL-SILICON LADDER CONCEPT**

### All-silicon ladder

- Single piece of silicon

- 4 sensors cut in one piece from the wafer

### **Post-processing of wafer**

Redistribution metal layers for data and power

Heterogeneous backside thinning

or

post-processing Polymer bulk silicon metal pads (AI) Flex cable Passive components Support structure ~1 mm 700 µm wafer Thinned to 400 µm Thinned to ~40 µm Support structure ~1 mm Demonstrator: Resistive heaters later: DMAPS sensors Bond pads RDL metal (Cu) Mounting hole ~100 µm gap ~ 30 mm 22 mm ~ 140 mm

RDL metal (Cu)

Polymer

ladder backside

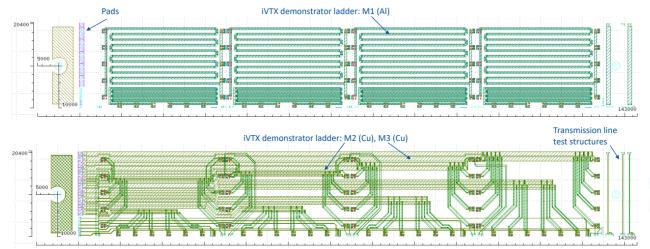

# **ALL-SILICON LADDER LAYOUT**

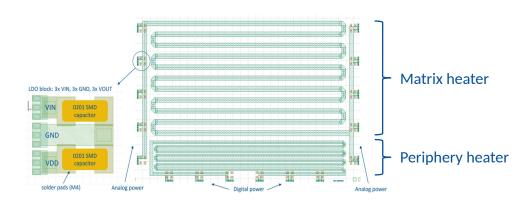

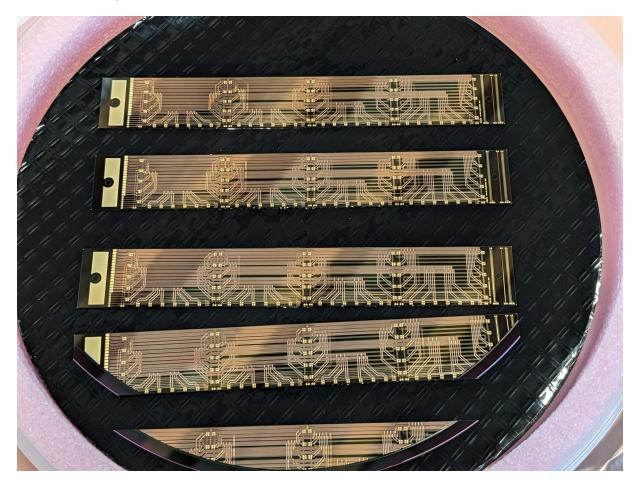

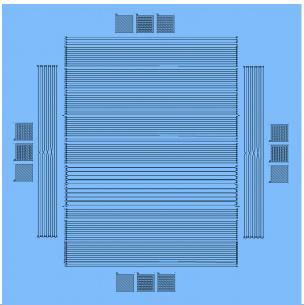

#### First RDL demonstrator with resistive heaters instead of CMOS sensors

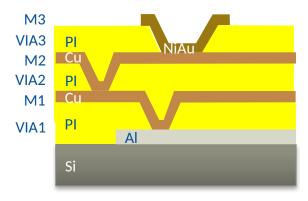

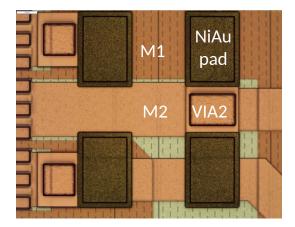

#### Metal system:

- Resistive heaters: 1.5 μm Al

- 2 RDL metal layers: 4 μm Cu

- Top metal finish: NiAu for wire-bonding, SMD soldering

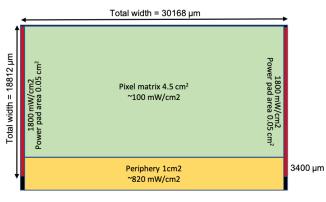

Ladder dimension:  $143 \times 20.4 \text{ mm}^2$ Dummy heaters (~10  $\Omega$ ):  $30 \times 20 \text{ mm}^2$

CMOS sensor example: Power domains, power pad locations

L1 might get a 3 chip ladder

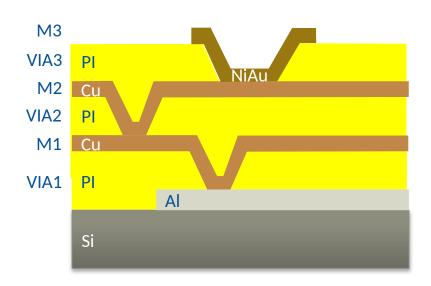

## ALL-SILICON LADDER PROTOTYPE FABRICATION

## Main fabrication steps:

- Alternating deposition of metal (3 μm Cu) and polymer (7 μm Polyimide)

- Photo lithography, wet chemical patterning

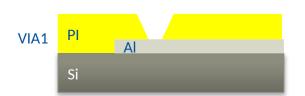

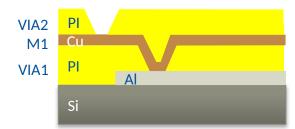

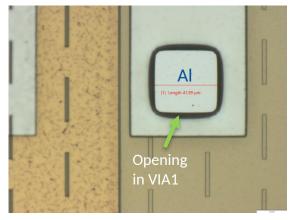

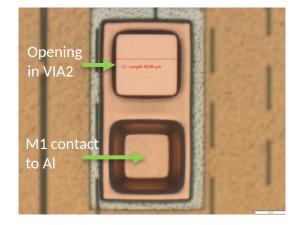

- First polymer layer "VIA1"

- Openings above sensor bond pads

- First RDL metal "M1"

- Contacts to sensor bond pads

- Second polymer layer "VIA2"

- Openings to M1

- Second RDL metal "M2"

- Contacts to M1

- Passivation layer "VIA3"

- Openings to M2

- NiAu bond pads "M3"

- Contacts to M2

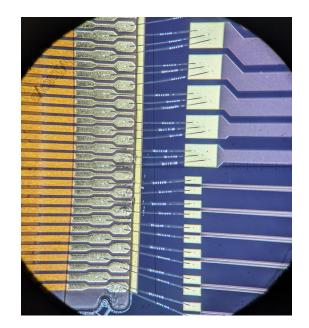

# **ALL-SILICON LADDER FABRICATION**

RDL process documentation of the first demonstrator produced by IZM Berlin

Characterization of layer topography, wafer flatness etc.

Pictures by IZM Berlin

# **ALL-SILICON LADDER DEMONSTRATOR**

First RDL demonstrators: 8 Wafers (725  $\mu m$ , 400  $\mu m$ , 300  $\mu m$ )

Production finished smoothly

# **ALL-SILICON LADDER DEMONSTRATOR**

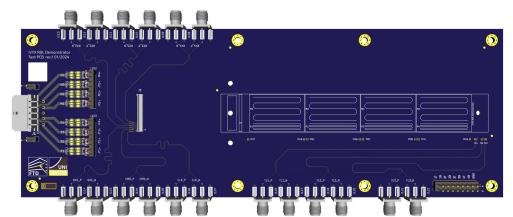

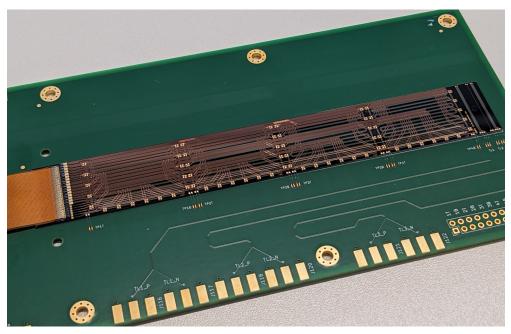

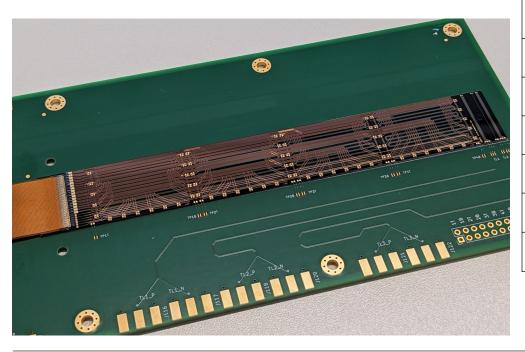

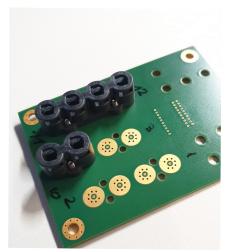

#### PCBs for electrical tests

- Configurable power routing and test points for I\*R drop measurements

- SMA connectors for differential lanes

- PCB mockups of the ladder for SMD soldering studies

# ALL-SILICON LADDER DEMONSTRATOR RESISTIVITY MEASUREMENTS

- Measured matrix resistance

- Measured Voltage and current to simulate power consumption

| Matrix | Resistance |

|--------|------------|

| M4     | 16.425 Ω   |

| M3     | 16.08 Ω    |

| M2     | 15.75 Ω    |

| M1     | 15.083 Ω   |

|                 | Matrix 4               |                      | Periphery 4          |

|-----------------|------------------------|----------------------|----------------------|

| V <sub>in</sub> | V <sub>meas</sub> (mV) | A <sub>in</sub> (mA) | A <sub>in</sub> (mA) |

| 500             | 437                    | 33                   | 31                   |

| 1000            | 873                    | 66                   | 61                   |

| 1500            | 1308                   | 98                   | 92                   |

| 2000            | 1744                   | 130                  | 122                  |

| 2500            | 2180                   | 162                  | 152                  |

| 3000            | 2617                   | 194                  | 182                  |

| 3500            |                        |                      | 211                  |

| 4000            |                        |                      | 240                  |

| 4200            |                        |                      | 251                  |

| Total           |                        | 508 mW               | 1054 mW              |

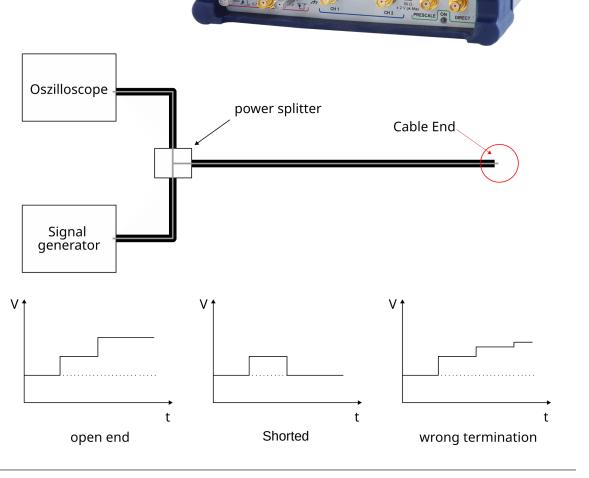

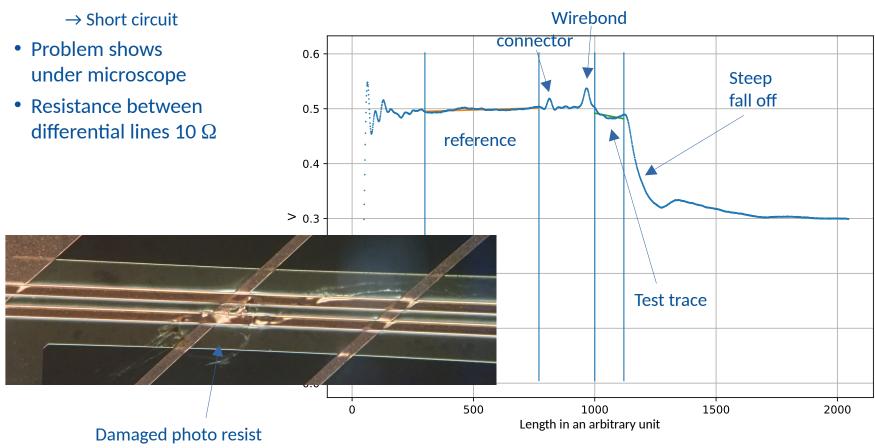

TIME DOMAIN REFLECTOMETRY

- Send electrical pulse and measure reflection

- Important is sharp edge at the beginning

- Method used to measure

- Cable length

- Defects

- Shorts

- Changes of impedance

- Etc.

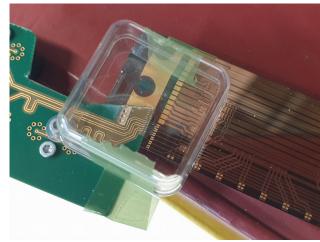

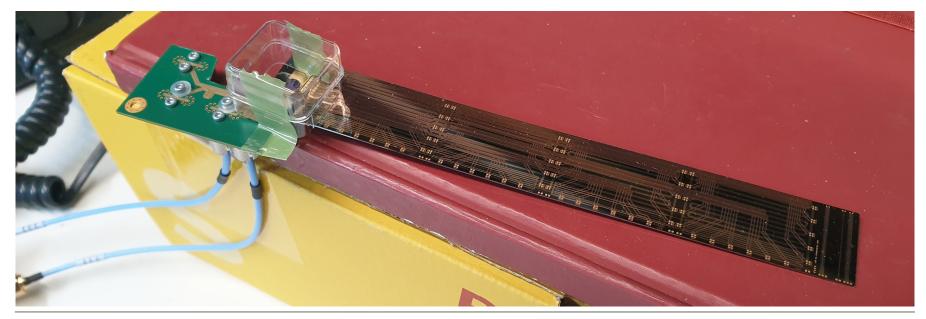

# TDR MEASUREMENT SETUP

- Cut old test PCB with high frequency connector

- Wirebonded PCB to test traces

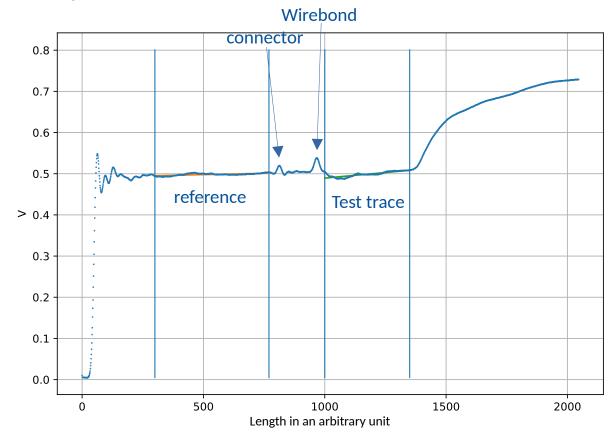

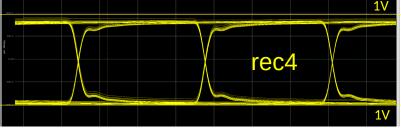

# TDR RESULTS ON GOOD TEST TRACE

- Average over cable as reference (100  $\Omega$ , differential)

- Fit linear eq. to trace to calculate impedance of trace

- Results:

- 96.4  $\Omega$  at beginning

- 104.4  $\Omega$  at end

- $100.2 \Omega$  average

#### **Reflection coefficient:**

$$\rho_{\text{test}} = (V_{\text{test}} - V_{\text{in}}) / (V_{\text{in}} - V_{\text{0}})$$

### Test trace impedance:

$$Z_{\text{test}} = Z_0 * (1 + \rho) / (1 - \rho)$$

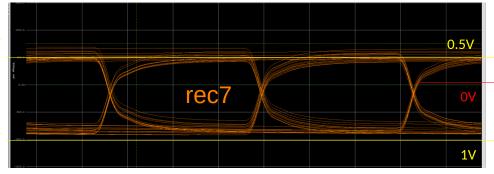

# TDR RESULTS ON BAD TEST TRACE

- Test trace seems to short.

- Impedance falls off at the end

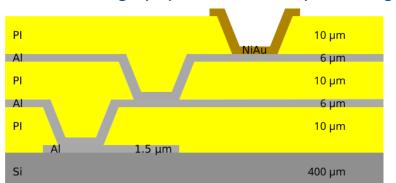

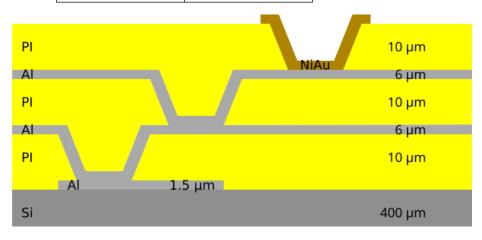

# ALL-SILICON LADDER SECOND PROTOTYPE FABRICATION IN FTD CLEANROOM

## Main fabrication steps:

- Alternating deposition of metal (6 μm Al) and polymer (10 μm Polyimide)

- Photo lithography, wet chemical patterning

conceptual

- First polymer layer "VIA1"

- Openings above sensor bond pads

- First RDL metal "M1"

- Contacts to sensor bond pads

- Second polymer layer "VIA2"

- Openings to M1

- Second RDL metal "M2"

- Contacts to M1

- Passivation layer "VIA3"

- Openings to M2

- (NiAu bond pads "M3")

- Contacts to M2

PI 10 μm

AI 6 μm

PI 10 μm

AI 1.5 μm

Si 400 μm

More realistic

# ALL-SILICON LADDER SECOND PROTOTYPE FABRICATION IN FTD CLEANROOM

- 1) Deposit first metal layer

- 2) Deposit photo resist for etching

- 3) Wet etching of aluminum

- 4) Application of polyimide photo resist

# ALL-SILICON LADDER SECOND PROTOTYPE FABRICATION IN FTD CLEANROOM

4) Application of polyimide photo resist

- 5) Baking of photo resist

- 6) repeat from 1)

# **ELECTRICAL TEST STRUCTURES**

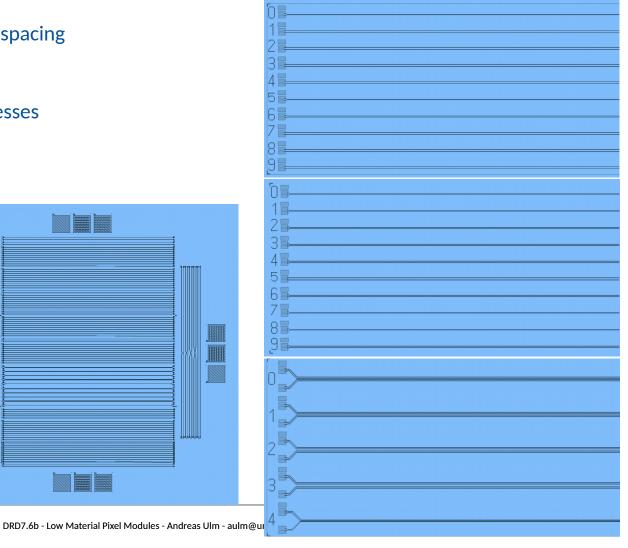

For better and more measurements we designed some test structures to test the properties of traces and our process:

- Different trace width and spacing

- Impedance matching

- Different polyimid thicknesses

- Crosstalk test structures

- Vias & Quality controll

- Capacities

- **Bond pads**

- Alignment

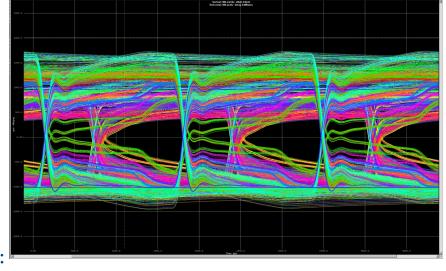

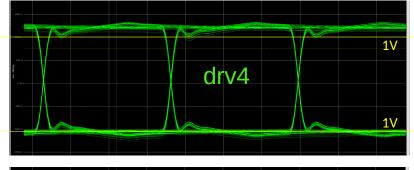

# **ELECTRICAL SIMULATIONS (PRELIMINARY)**

### Trace design originates from simulation:

- Important features are:

- Impedance matching

- Rise time of signal edge

- Signal loss over trace

- Simulation set to

- 600 Mbps

- 1V

- differential

Some examples

(arbitrary names):

Rec7 shows a lot of amplitude loss over a 10 cm trace, even though the eye still looks ok

Rec4 shows a pretty nice example. A wide open eye with max and min voltage around 1V (input voltage).

# MATERIAL BUDGET

## The contributions to Material Budget:

#### Main contribution Silicon:

| 400 μm | 0.427% X <sub>0</sub> |

|--------|-----------------------|

| 300 μm | 0.32% X <sub>0</sub>  |

| 100 μm | 0.107% X <sub>o</sub> |

Assuming homogeneous distribution over whole ladder. As structuring leads to places with no/less Al, the material budget will be lower.

#### RDL Contibutions:

| Material | Thickness | X <sub>o</sub>         |

|----------|-----------|------------------------|

| Copper   | 3 μm      | 0.021% X <sub>0</sub>  |

| Aluminum | 6 μm      | 0.0067% X <sub>0</sub> |

| Polyimid | 10 μm     | 0.0035% X <sub>0</sub> |

| NiAu     | 100 nm    | 0% X <sub>0</sub>      |

#### RDL total:

| Material | Thickness | X <sub>0</sub>         |

|----------|-----------|------------------------|

| Aluminum | 2 x 6 μm  | 0.0135% X <sub>o</sub> |

| Polyimid | 2 x 10 μm | 0.007% X <sub>0</sub>  |

| Total    | 32 μm     | 0.0205% X <sub>0</sub> |

For Cu RDL: 0.0488% X\_0 in total

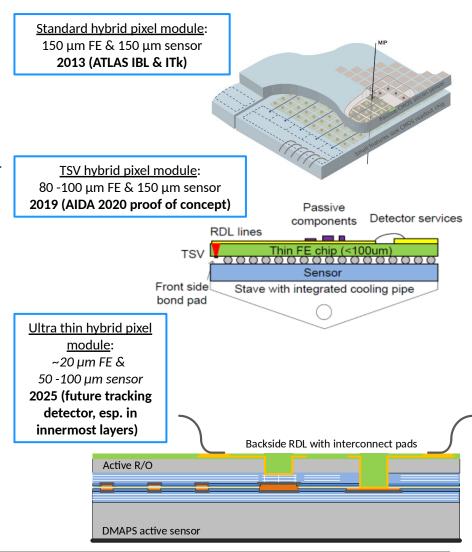

## ULTRA THIN HYBRIDS CONCEPT

- Want to reduce mass, i.e. thickness of pixel detectors as much as possible while keeping the benefits of the hybrid approach:

- Separate development and optimization of sensors and FE electronics allowing for best performance of FE electronic and sensor.

- Fine pitch interconnection between FE and sensor pixel with a pitch down to  $\sim 20 \mu m$ .

- Thinning of FE and sensor parts to the minimum.

- Can benefit from active CMOS sensor development by integrating some electronic already into the sensor

- Target is the development of ultra-thin hybrid pixel detectors based on:

- 50 100 μm thick pixel sensor on 200 (300) mm CMOS wafers

- ~20 μm thick pixel FE chip thickness on 200 (300) mm CMOS

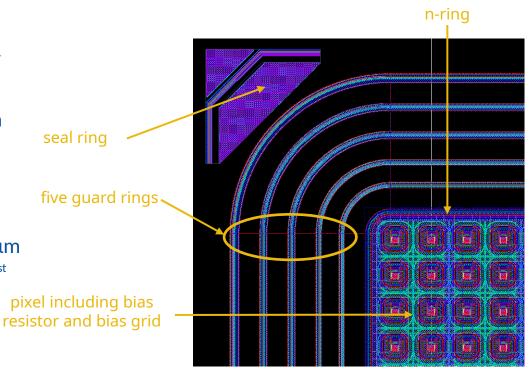

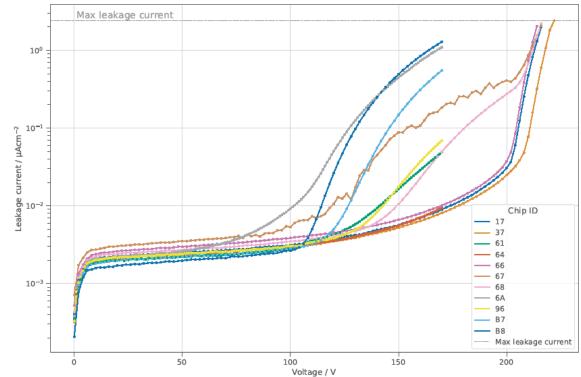

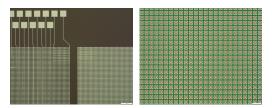

## **CMOS PIXEL SENSOR DESIGN**

- Strategy: "copy" layout from former passive CMOS submissions at LFoundry:

- Match pixel size with TimePix3 pixel size →

55 μm pixels

- Increase n-well size to 35 um → keep 8 μm spacing between n-well and p-stop

- Poly-silicon bias resistor implemented (and bias grid)

- N-ring surrounding the pixel matrix → 32 μm spacing between n-ring and p-well (from 1<sup>st</sup> guard ring)

- Five n<sup>+</sup>p guard rings

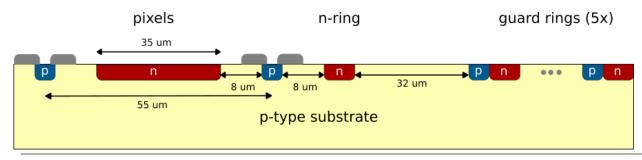

# **CMOS PIXEL SENSOR FABRICATION**

- Fabrication of sensor wafers done in 2024 at LFoundry with an engineering run

- 23 sensor wafers delivered in late 2024

- Wafers are now at IZM for postprocessing

- 2 wafers have been processed with backside metallization and front side handling wafer removal

- Visual inspection showed no obvious issues

- Wafer are shipped to Bonn and Dortmund for sensor testing

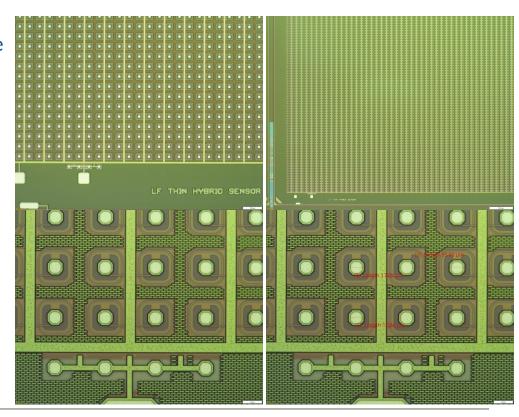

## CMOS PIXEL SENSOR FIRST TEST

LF Thin Hybrids

First wafer (???)

- The first measurements were carried out on 11 evenly distributed chips

- The bias grid was grounded, and the N-ring remained floating

Contact with the chips was made manually

- slow process!

Breakdown occurs at ~ 200 V for chips tested up to 300 V

### Sensors work as expected!

More testing planned at Bonn & Dortmund

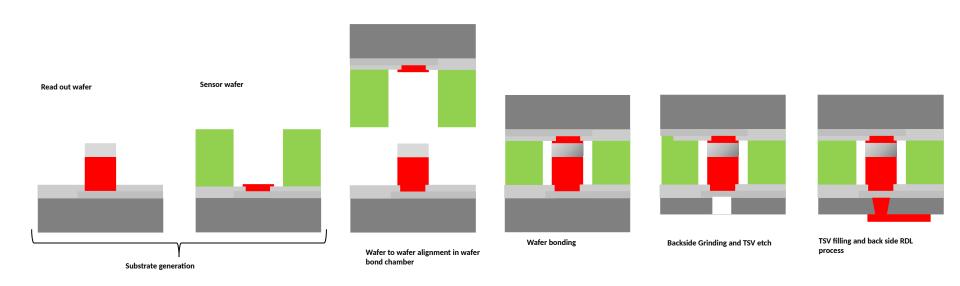

## **GENERAL PROCESS FLOW**

- The Cu/Sn wafer bonding is a well established process

- The Cu/Sn bond will be supported by spin coated, photo-structured polymer layer which is joined simultaneously (polymer hybrid wafer bonding)

- Depending on total wafer stack thickness a mechanical support during TSV formation and backside RDL process will be required

# WAFER TO WAFER BONDING - PROCESS EVALUATION

W2W bonding setup bottom wafer:

RDL Design

RDL Design

UBM + Bondlayer top wafer

Bottom wafer with Cu-SnAg pillar

- Three wafer stacks for evaluation:

- Planar Glass-Si wafer: optical bonding interface characterization (fast track)

- Planar Si-wafer with UBM: polymer bonding with topography wafer

- 3) Daisy-chain-test wafer (silicon to silicon): bonding process evaluation with focus on polymer layer thickness – Pillar/UBM height tolerances

#### W2W bonding setup top wafer:

Top wafer with Cu-Pad and polymer layer

#### **Process Development Goal:**

Evaluation of a bonding material that enables the combination of a polymer glue bonding process with the Cu-SnAg pillar bonding process

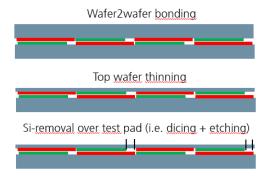

# WAFER TO WAFER BONDING - PRELIMINARY RESULTS

#### **Preliminary Process Results:**

- Process evaluated for 20μm polymer layer thickness, measured bond layer thickness: 21μm (+/- 0.5μm across the wafer)

- Pillar height: 13...15μm (as plated) (tolerances across the wafer)

Cu pad height: 5.5μm (+/- 0.5μm across the wafer)

- Thinning of top wafer to 80µm thickness possible

- Dicing of wafer stack possible

- Low adhesion between top and bottom chip after dicing (chips can be easily debonded)

- Large area solder transfer from CuSnAg-pillar (bottom chip) to Cu pad (top chip) visible after top chip debonding but some pillars are not connected to Cu pads (see cross section)

- Bonding without additional pillar bumps planarization suffers from total height variations across the wafer

Planarization

• → Solution: Development of Pillar-Planarization Process

Cu-Sn Pillar

cross section after W2W bond (1000x):

Top and bottom pillar shifted due to

missing alignment marks on short loop test

wafers but formation of interconnects are

as expected

cross section after wafer to wafer bonding:

Left: slightly connected pillars, solder transfer to Cu pad (top) visible Right: gap between pillar and pad, no solder transfer to Cu pad (top)

Polymerlayer

W2W bond

## W2W BONDING - PROCESS EVALUATION SUMMARY

#### **Conclusions:**

- Lateral dimension (x, y) of bonding structures are sufficient to handle the W2W alignment tolerances (pad-, pillar-, polymer-via diameter)

- Very narrow tolerances in z-direction: pad pillar polymer thickness must and can be optimized by pillar-polymer layer planarization

### Status and next steps for process definition and design of the final object:

- Adaption of process flow including TSV and RDL formation done

- Process step definition fixed

- Individual pixel side design finished (polymer bonding layer and pillar design for readout and sensor wafer)

- W2W bonding alignment mark configuration fixed

- Discussion on TSV and TMPX3 TSV and backside RDL ongoing (CERN, IZM, Bonn University)

- LFoundry DMAPS wafer (thickness 150 μm) in process:

- Backside metallization on LF sensor wafer finished

- Debonding of pixel side carrier wafer (from LF processing) ongoing

- Next step: start of wafer processing for W2W bonding (backside carrier bonding, polymer layer, pillar formation and planarization)

### **SUMMARY**

- All-Silicon Module approach viable for CMOS sensors with high yield

- Big reduction of material budget when air or contact cooled

- Relatively easy and somewhat cheap to produce

- Currently optimizing RDL layers for signals and power

- Thin Hybrid Modules combine advantages of low material budget and independent development of sensor and FE chip

- Possibility to combine concept with All-Silicon approach to reduce material even further

- Currently developing reliable wafer to wafer bonding process