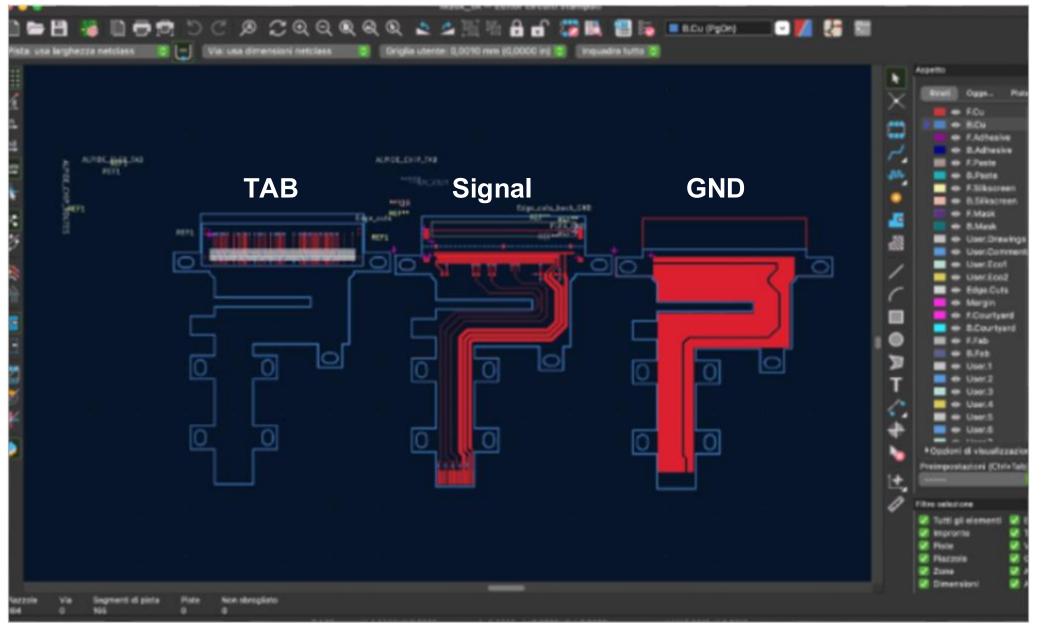

## Low mass Aluminium Flex Platform From KiCAD to KLayout design

## Low mass Aluminium Flex Platform From KiCAD to KLayout design

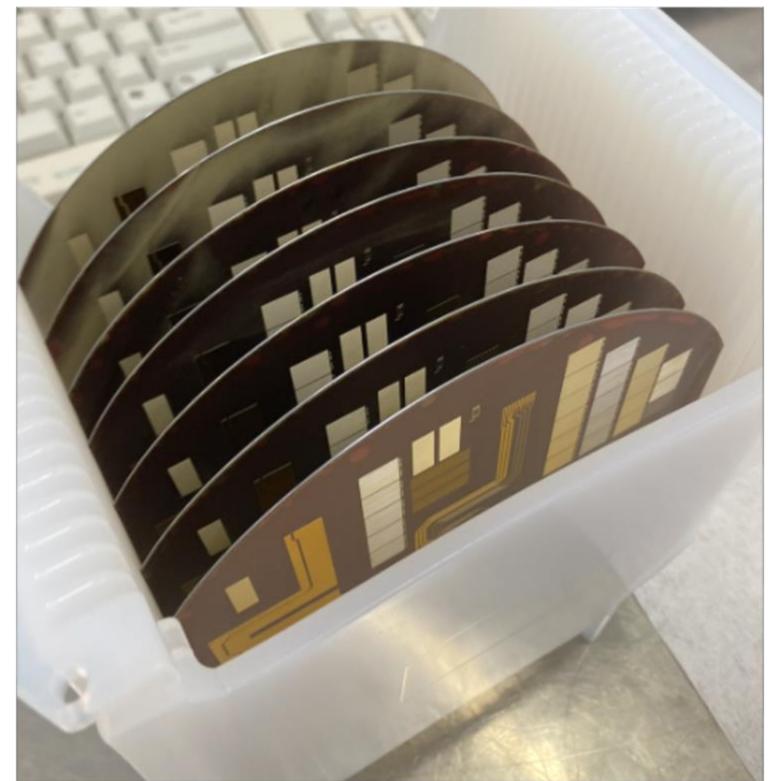

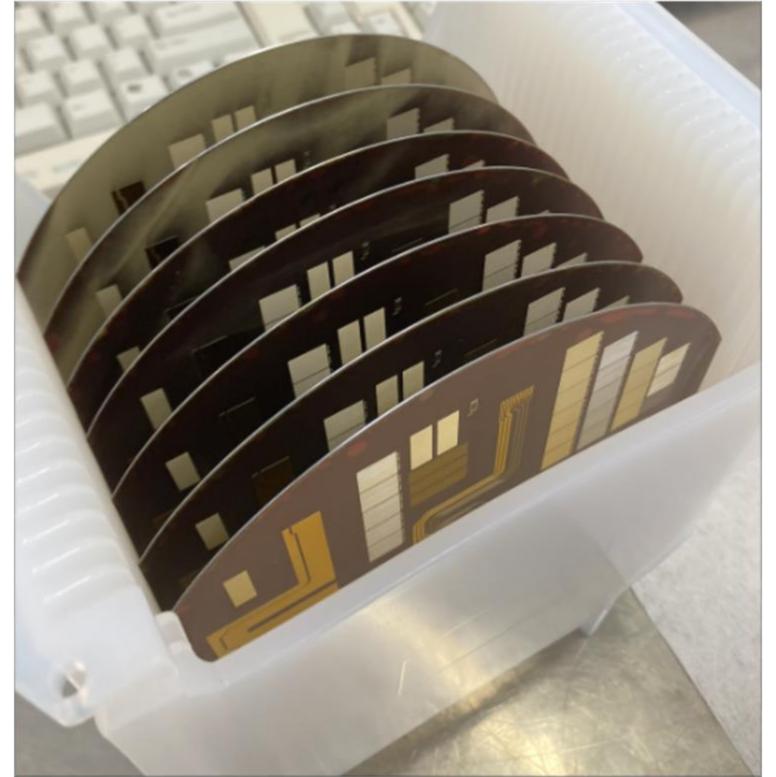

## Low mass Aluminium Flex Platform Wafer-level manufacturing

#### **Low mass Aluminium Flex Platform**

Wafer-level manufacturing

page

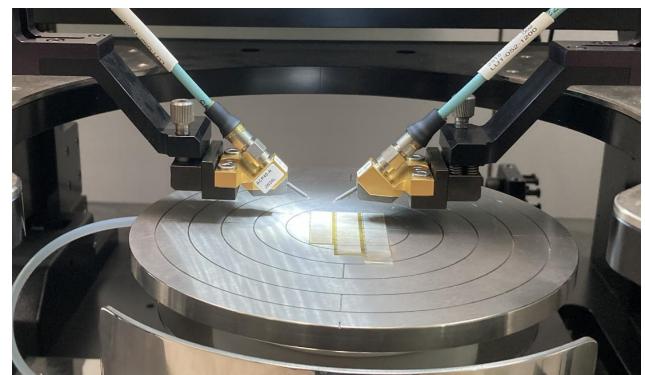

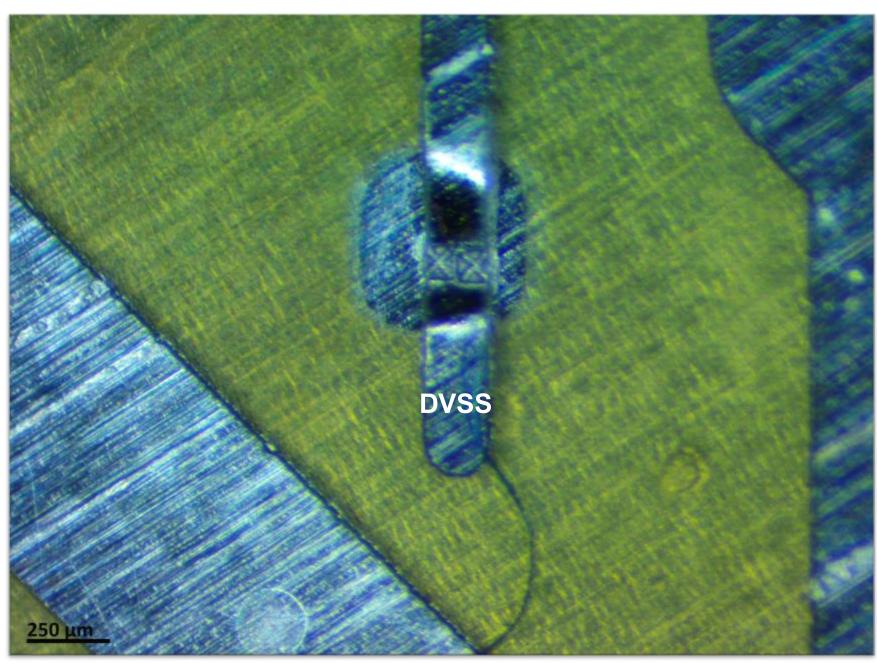

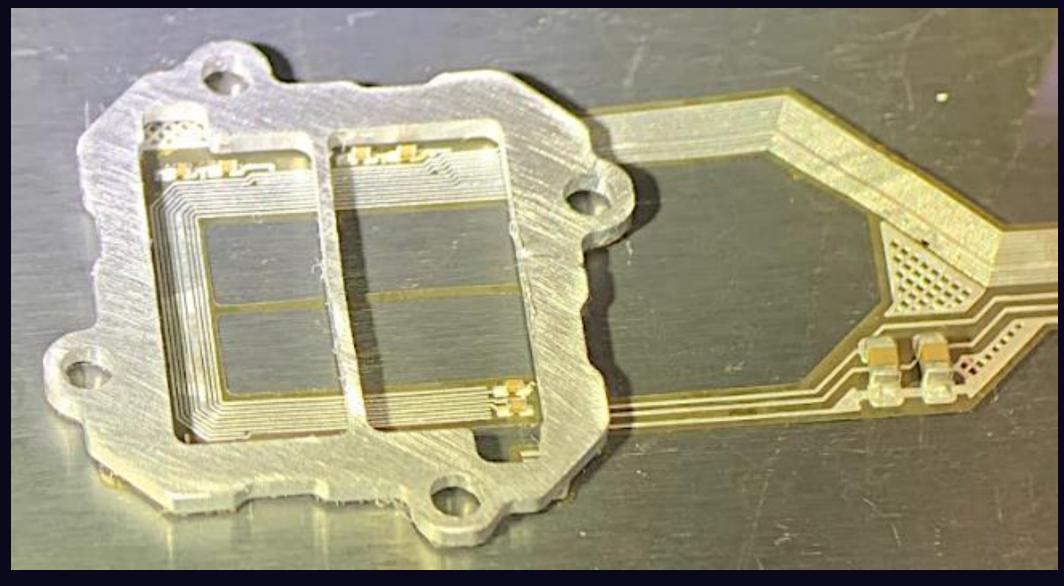

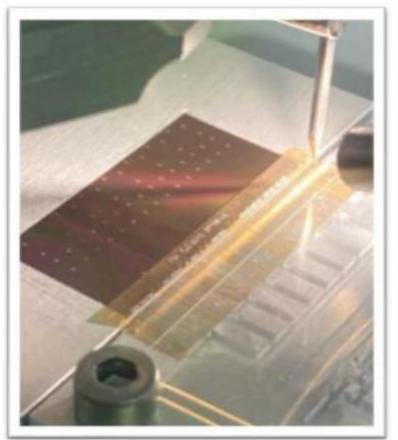

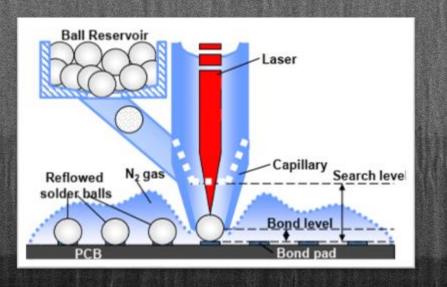

#### Low mass Aluminium Flex Platform Single Point Tape Automated Bonding

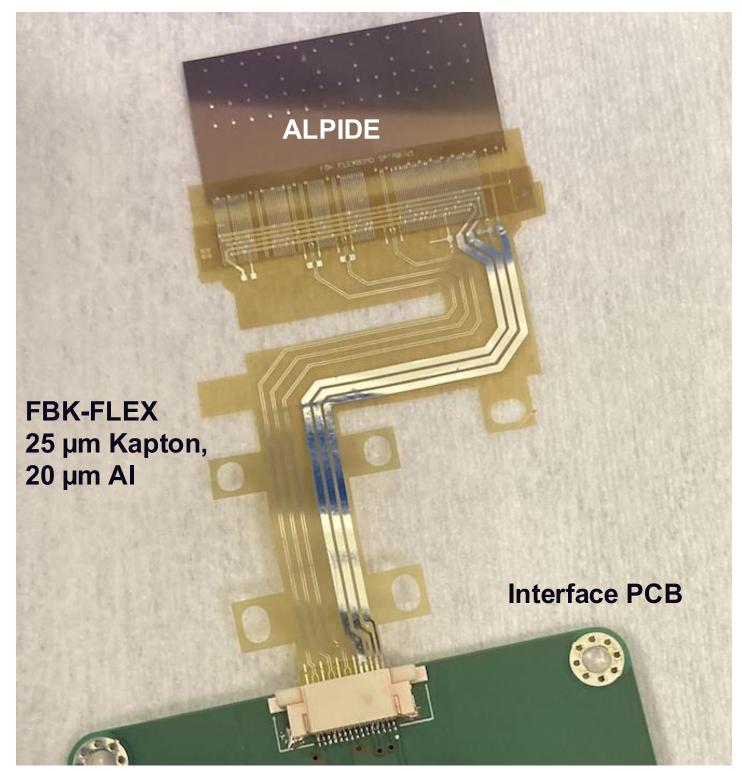

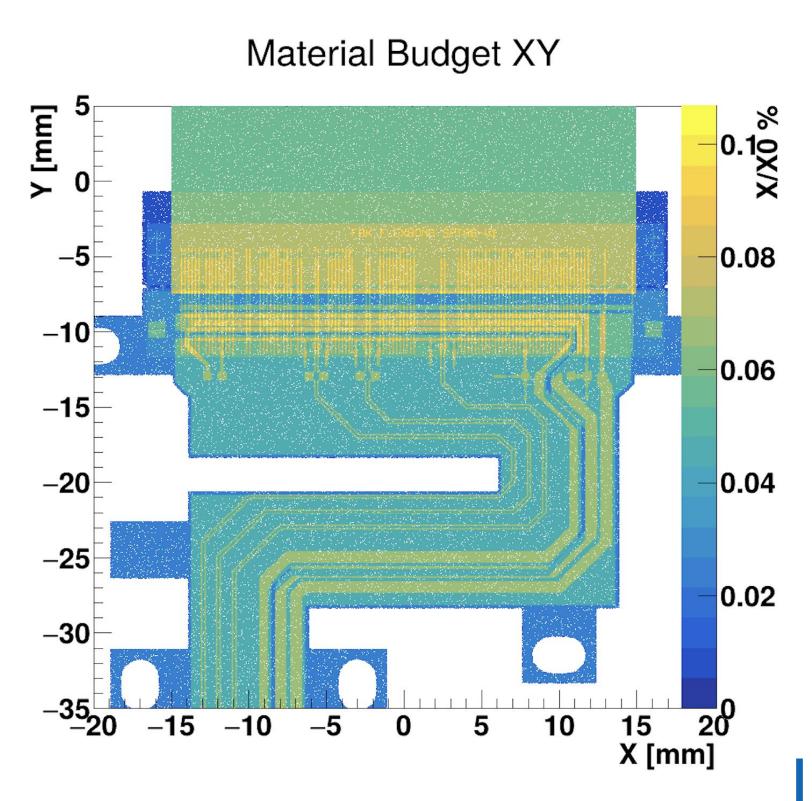

## Low mass Aluminium Flex Platform Final PCB and Material Budget

#### **Low mass Aluminium Flex Platform**

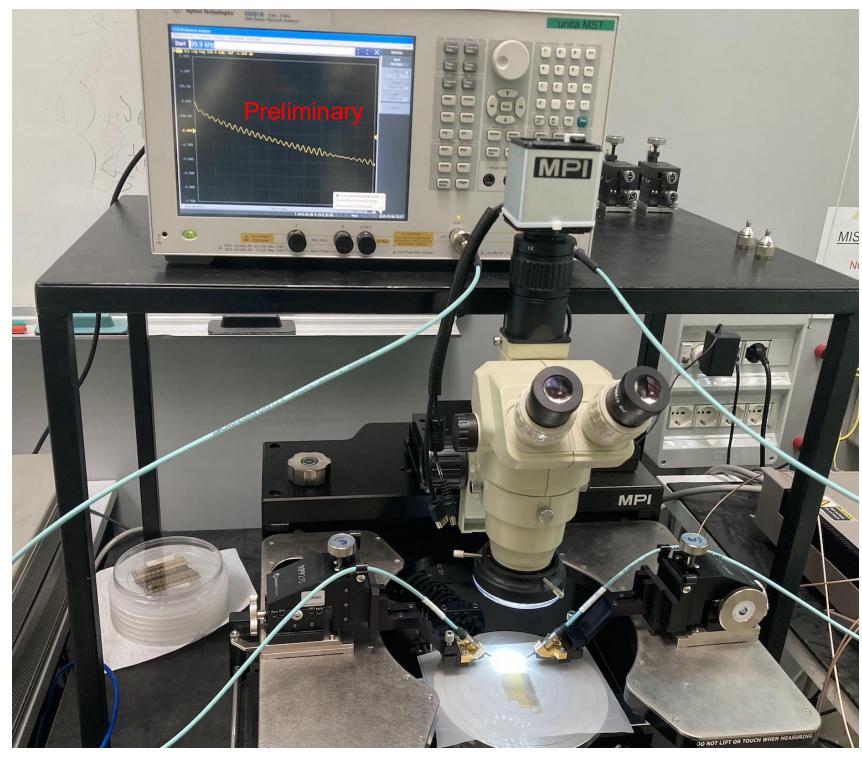

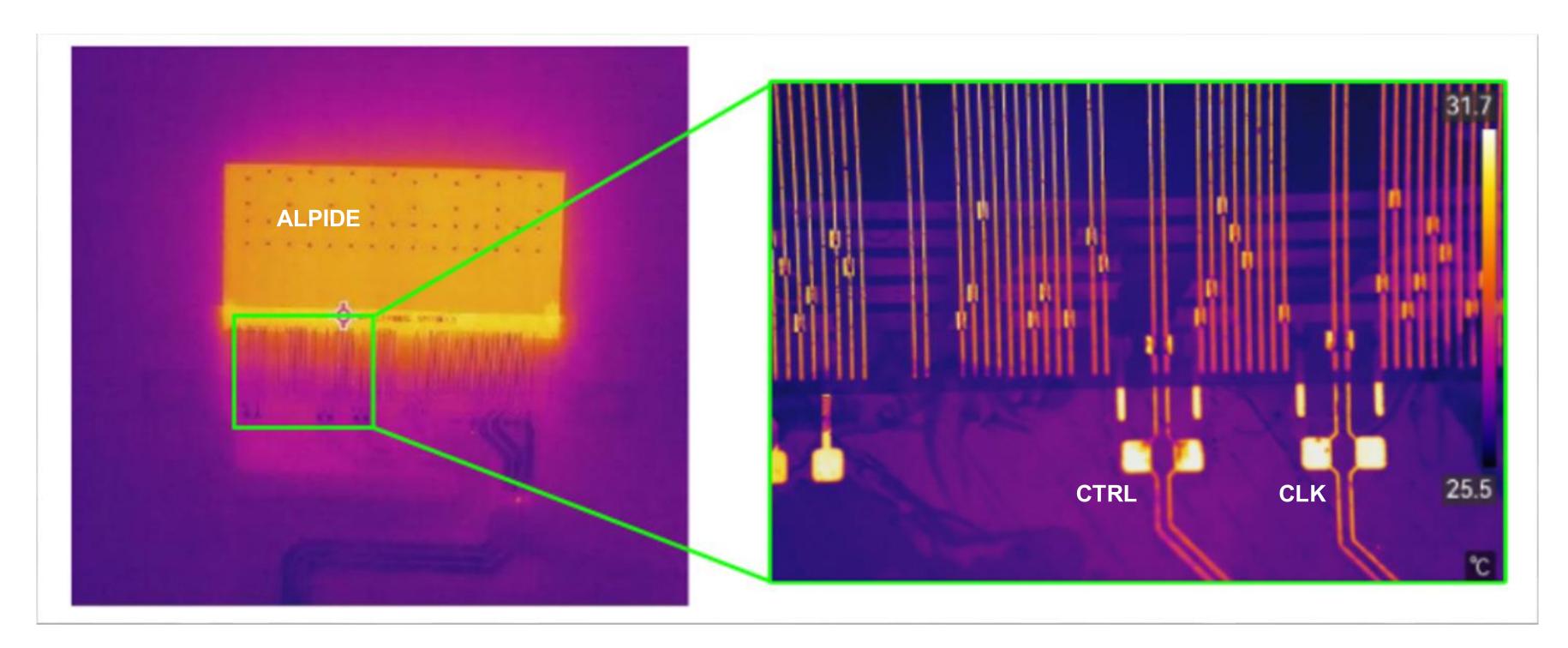

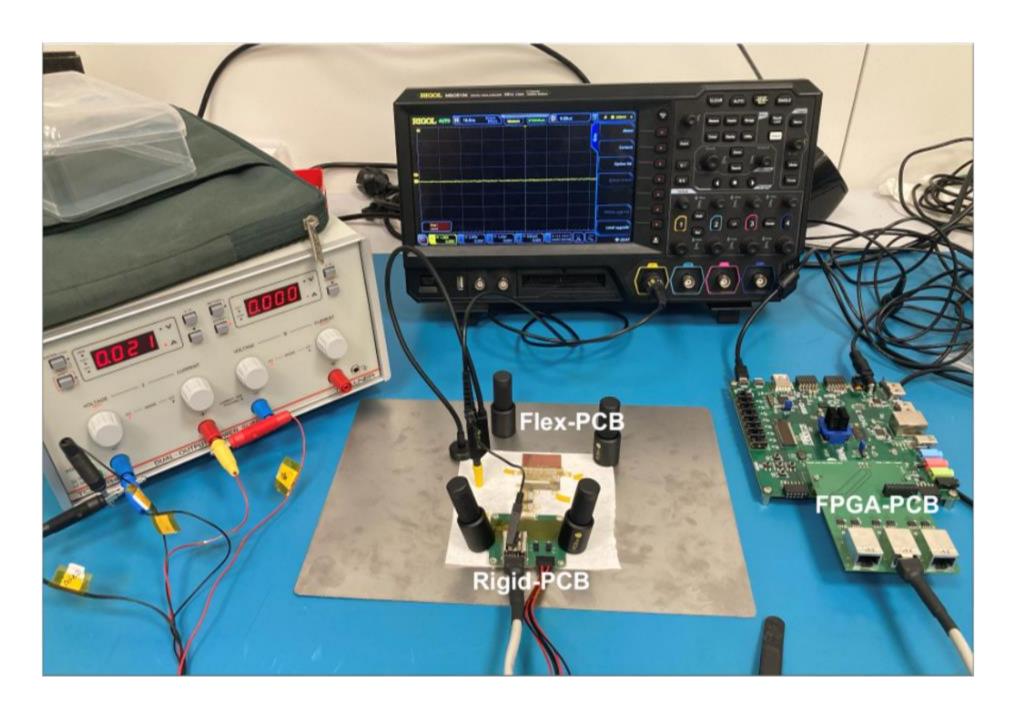

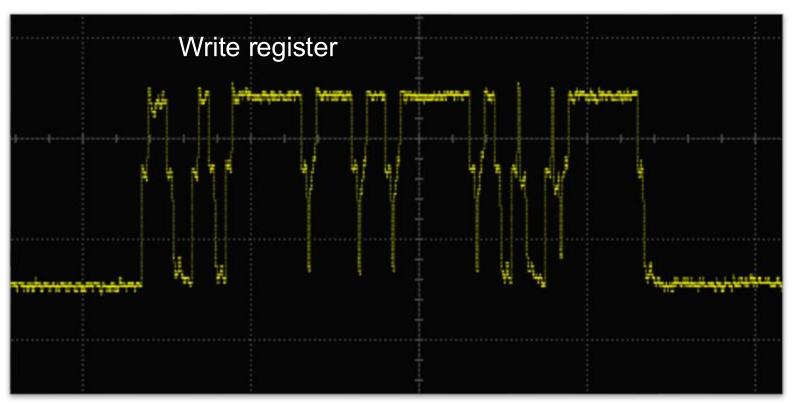

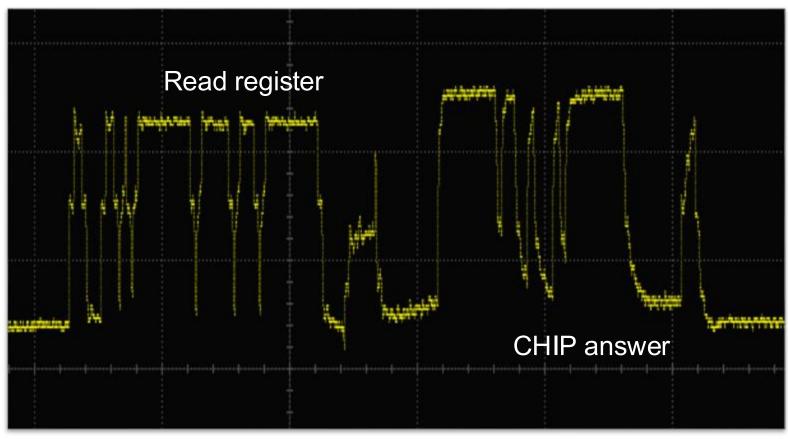

#### Electrical/thermal testing on ~50 samples

## Low mass Aluminium Flex Platform Electrical/thermal testing

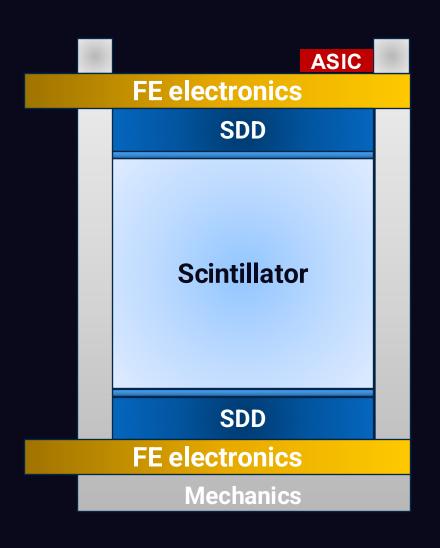

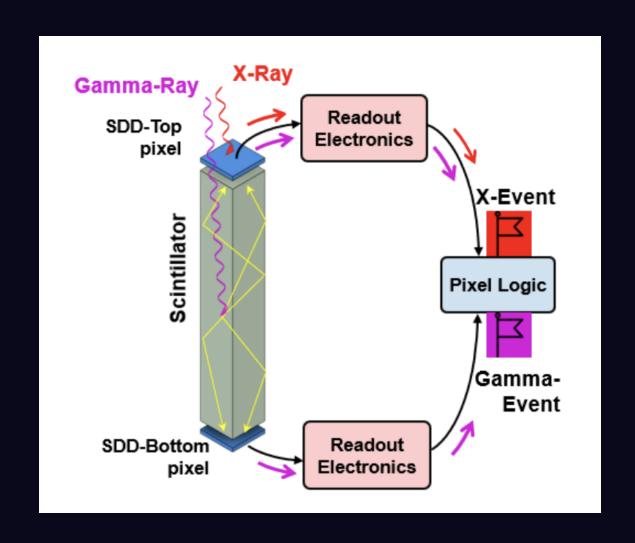

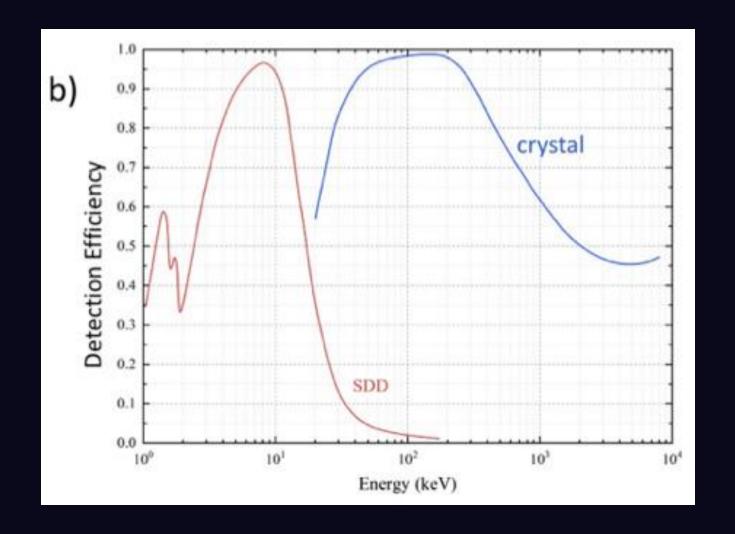

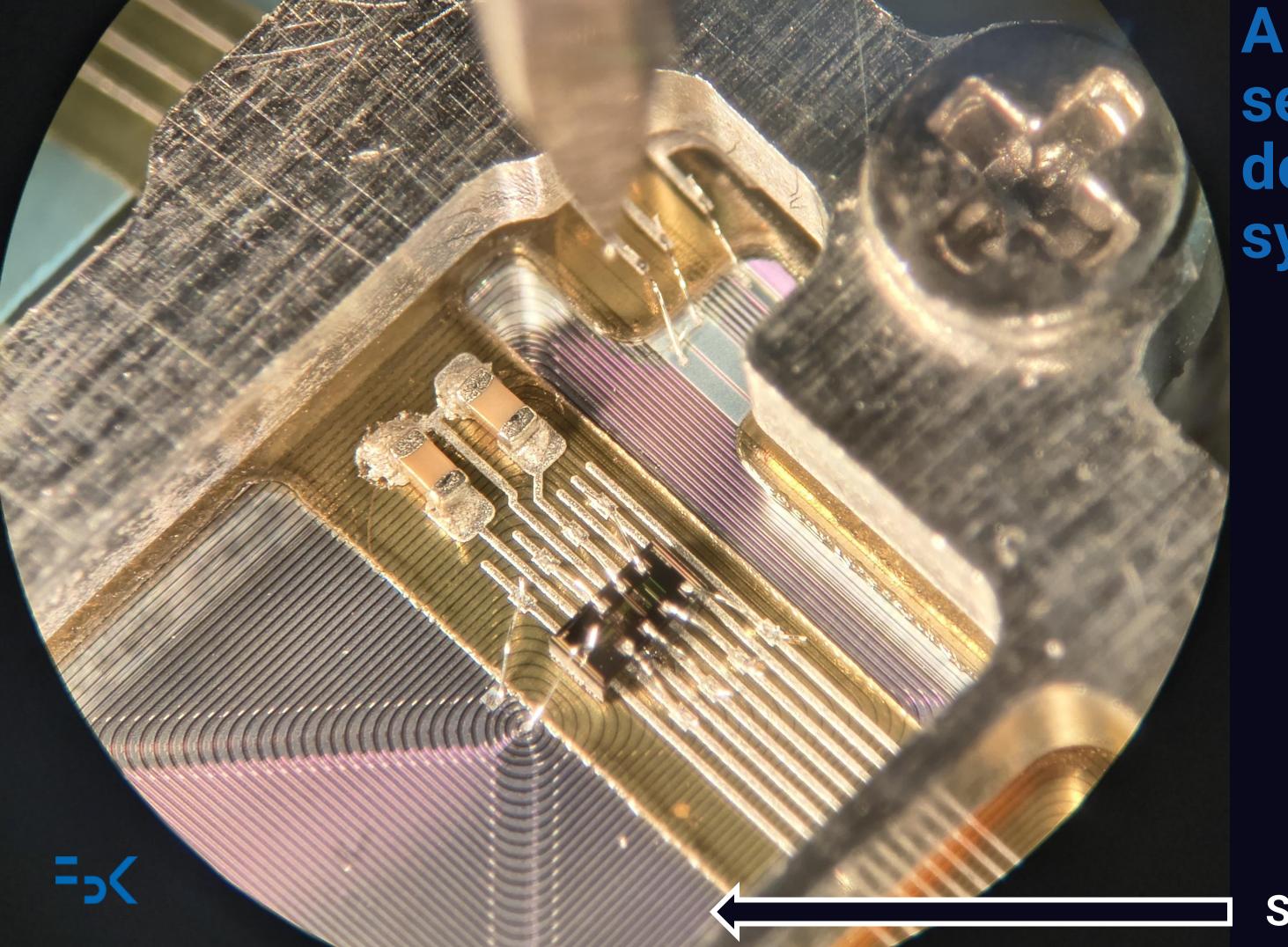

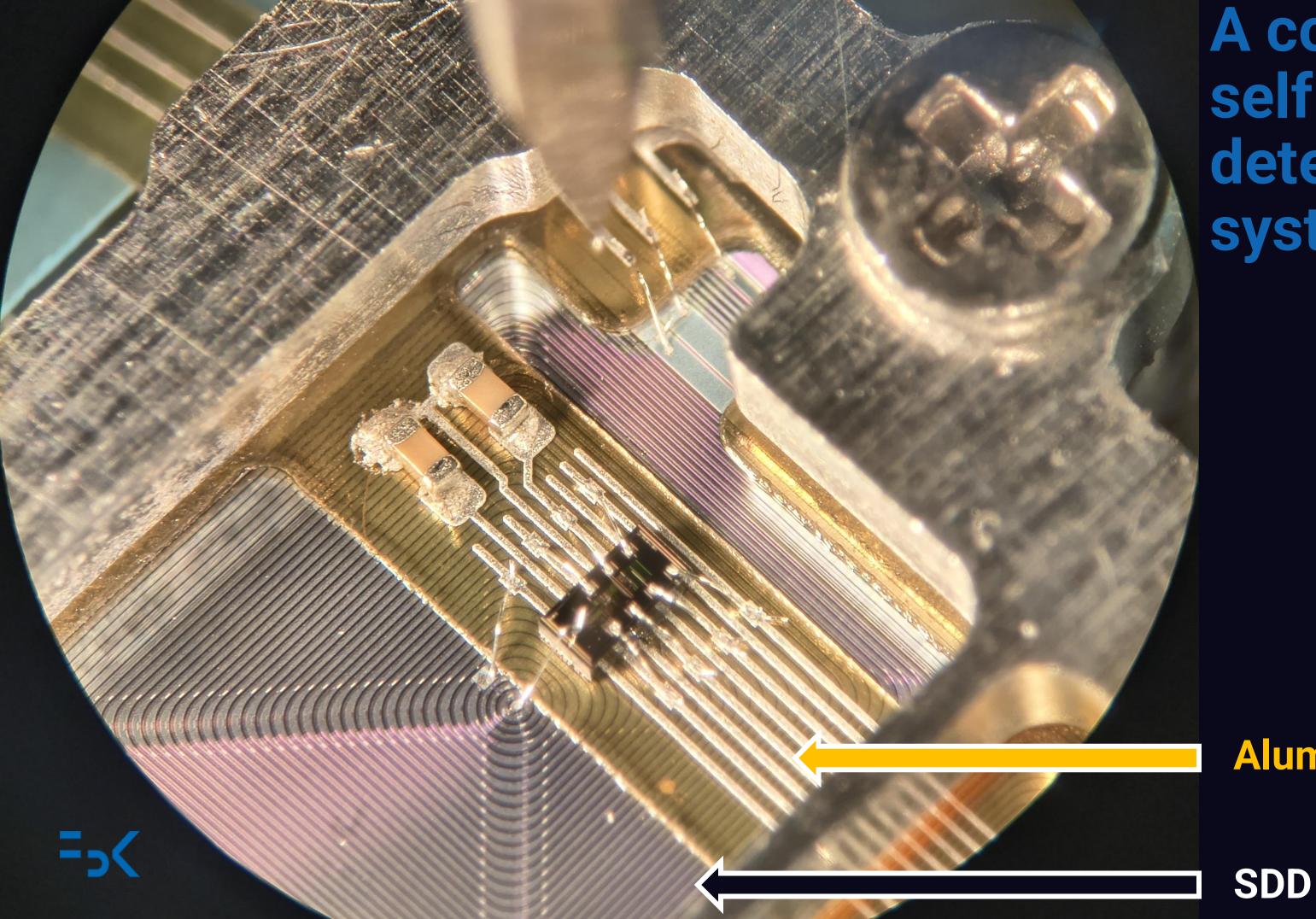

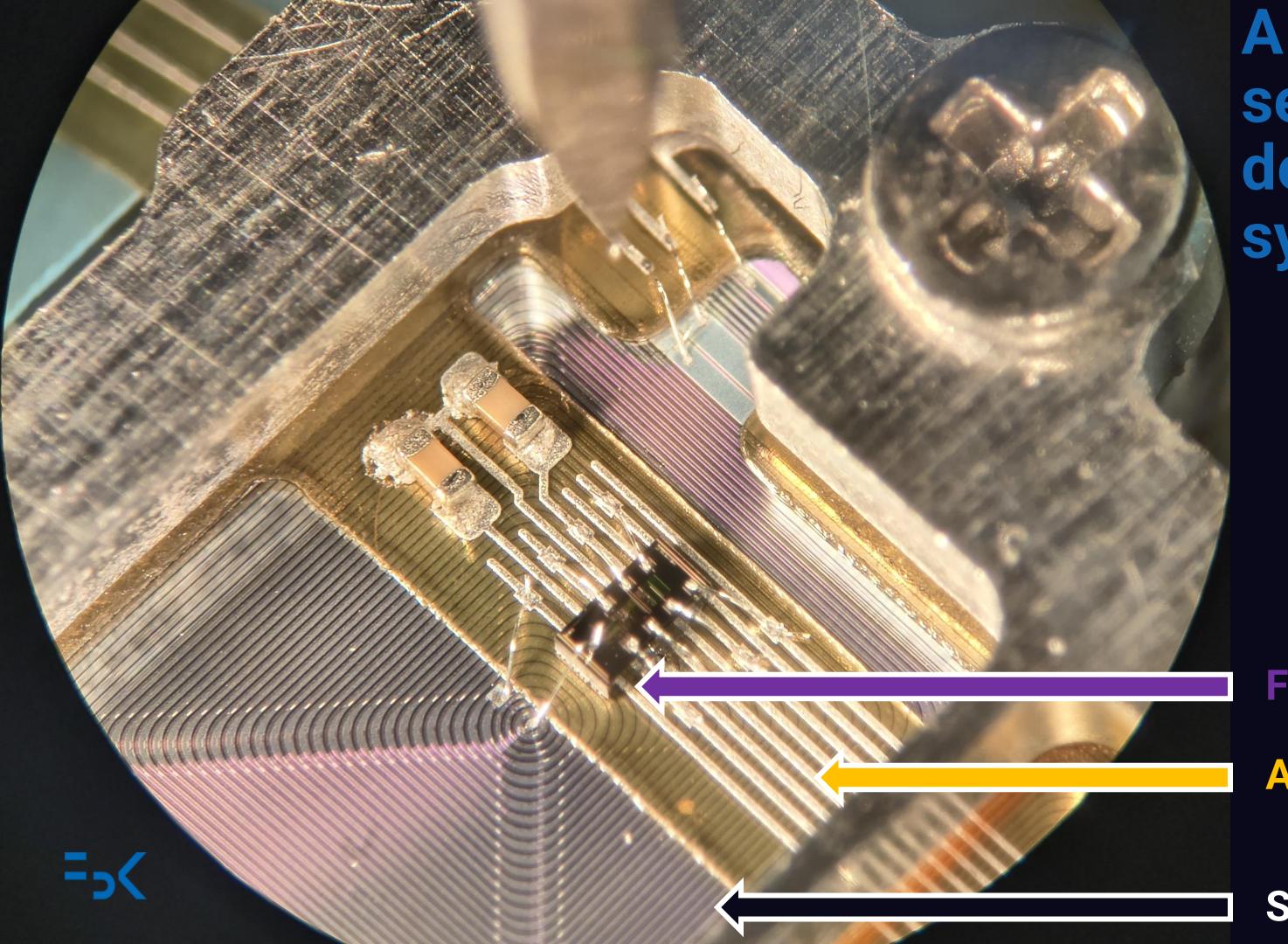

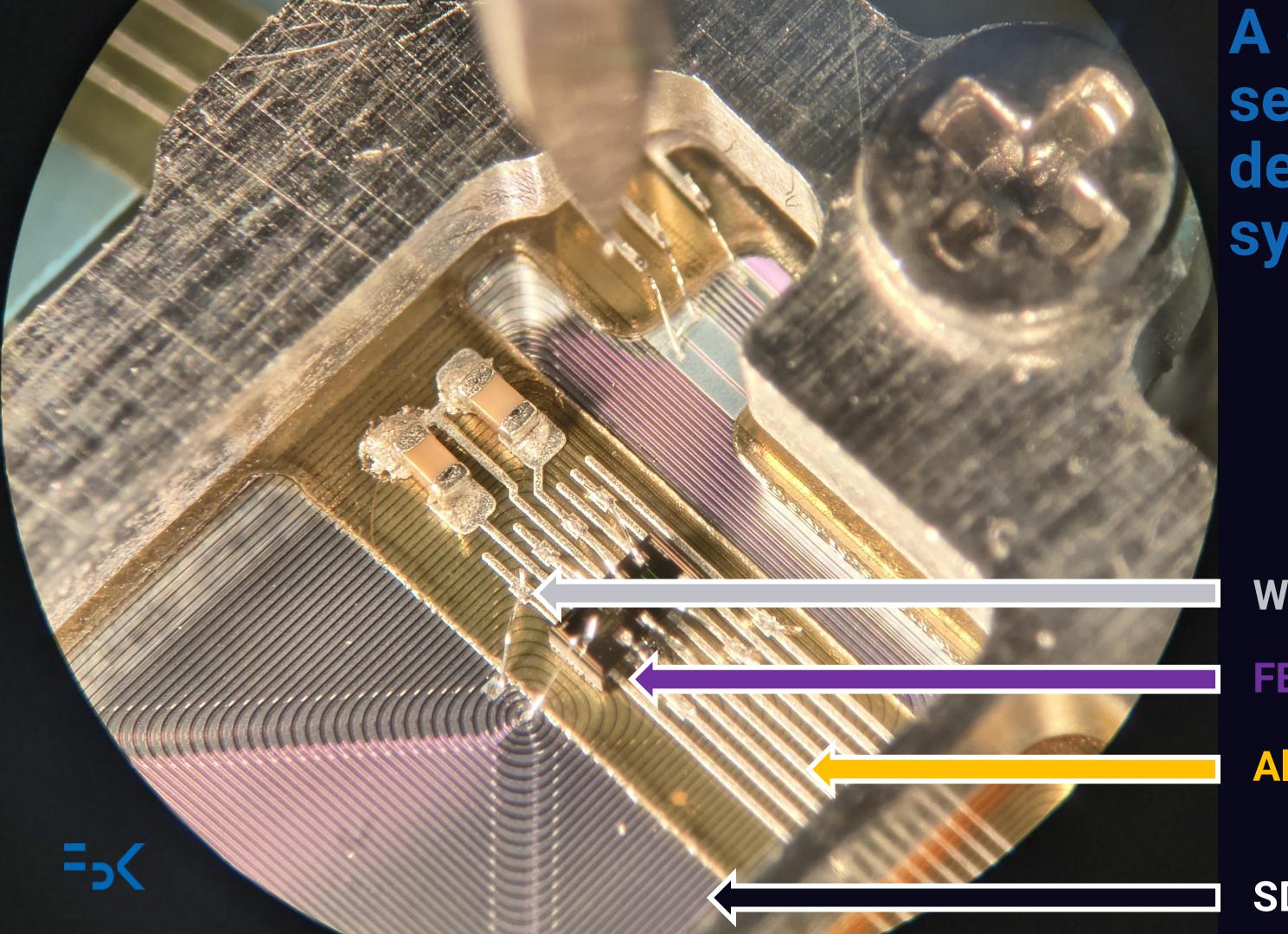

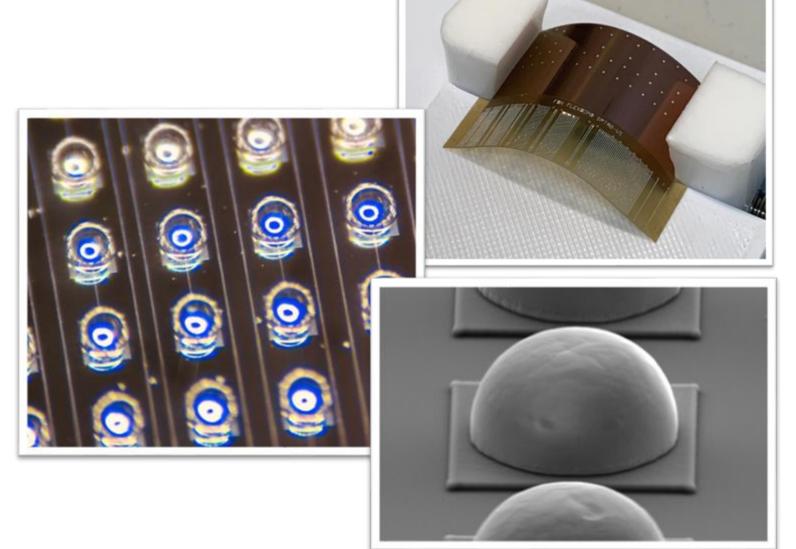

### 2x2 detector system for X-ray and γ detection

Developed by the REDSOX Collaboration [1]

### 2x2 detector system for X-ray and γ detection

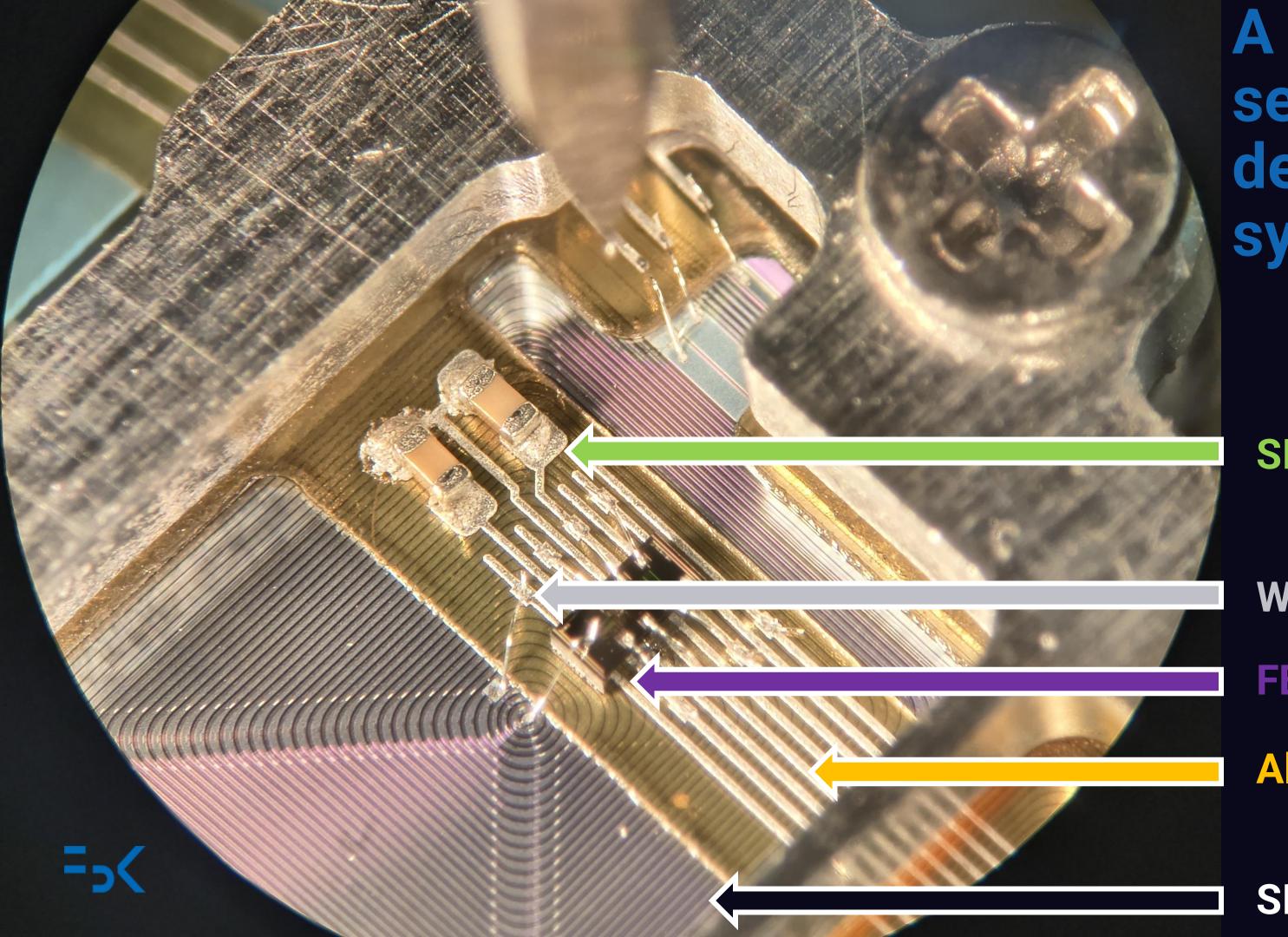

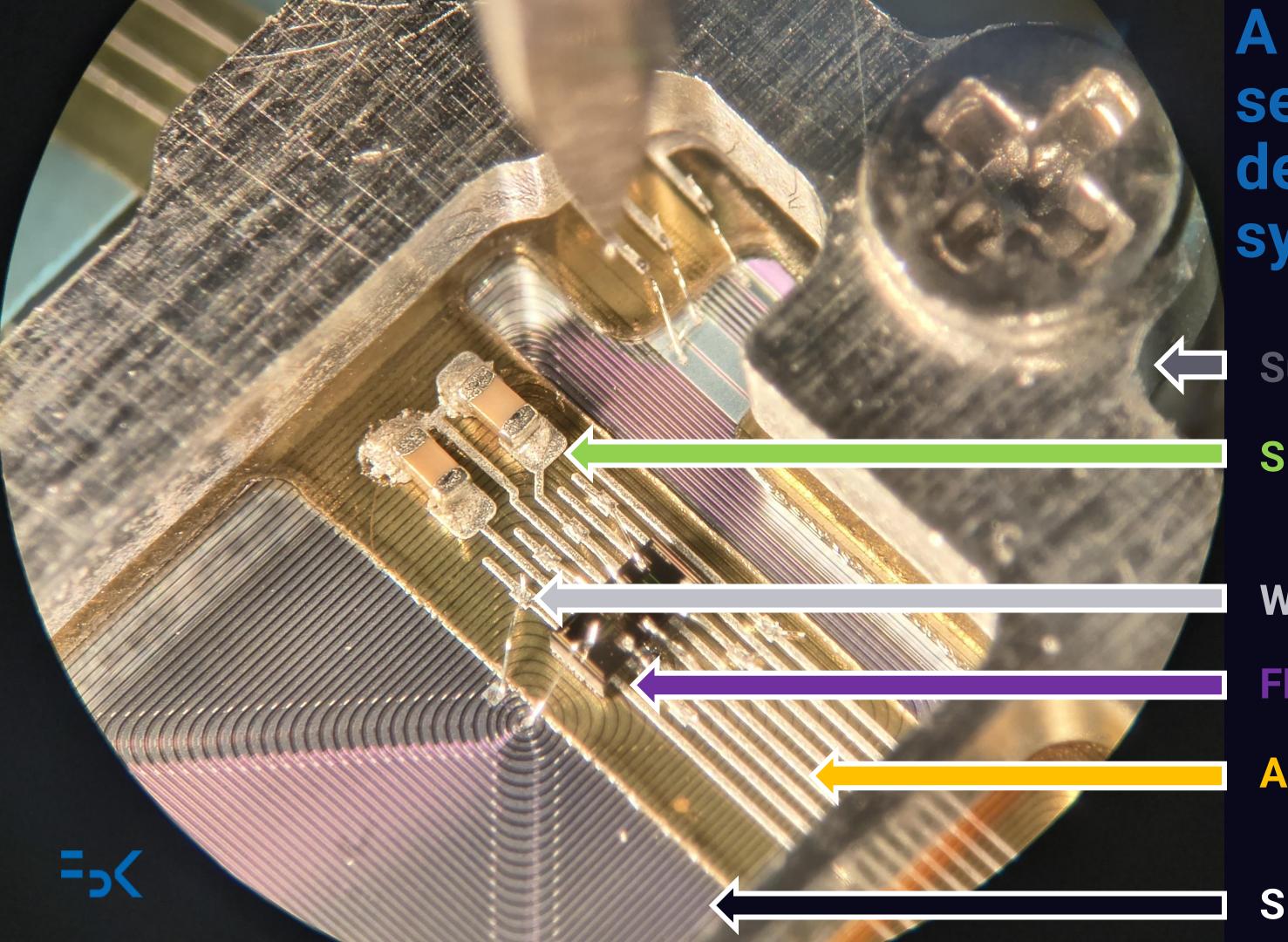

## spTAB?

## Wire bonding?

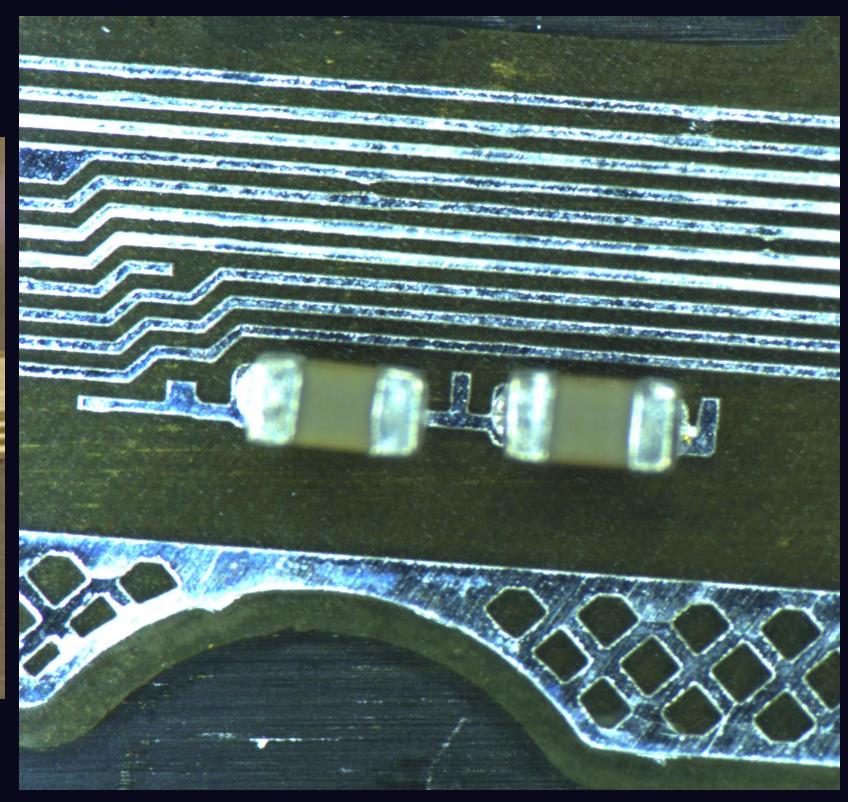

## Can SMDs be mounted?

Yes

page 013

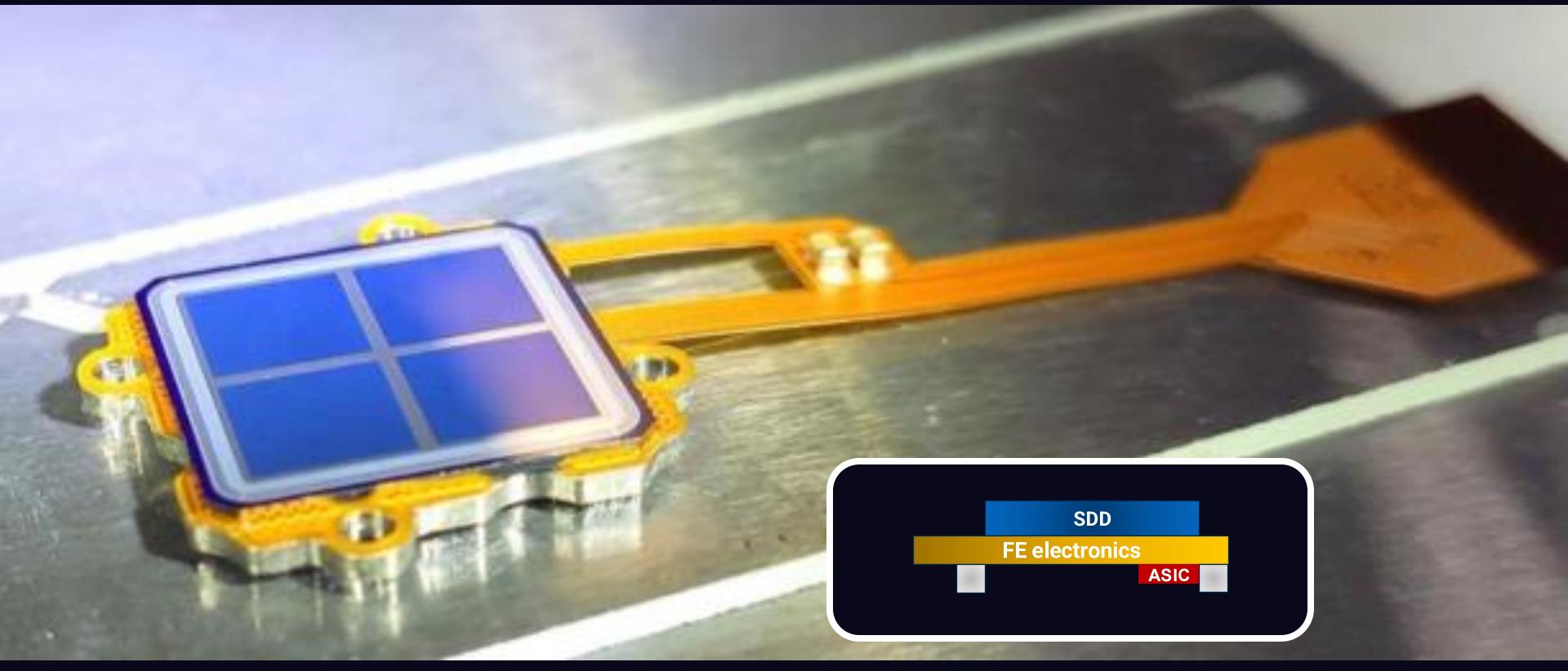

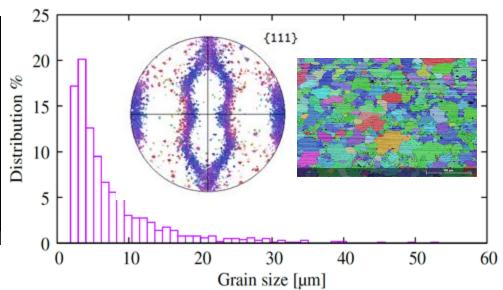

**Aluminum Flex**

page 013

FE ASIC

**Aluminum Flex**

page 013

**Wire Bonding**

**FE ASIC**

**Aluminum Flex**

page 013

**SMDs**

**Wire Bonding**

**FE ASIC**

**Aluminum Flex**

page 013

**Support Mechanics**

**SMDs**

**Wire Bonding**

**FE ASIC**

**Aluminum Flex**

page 013

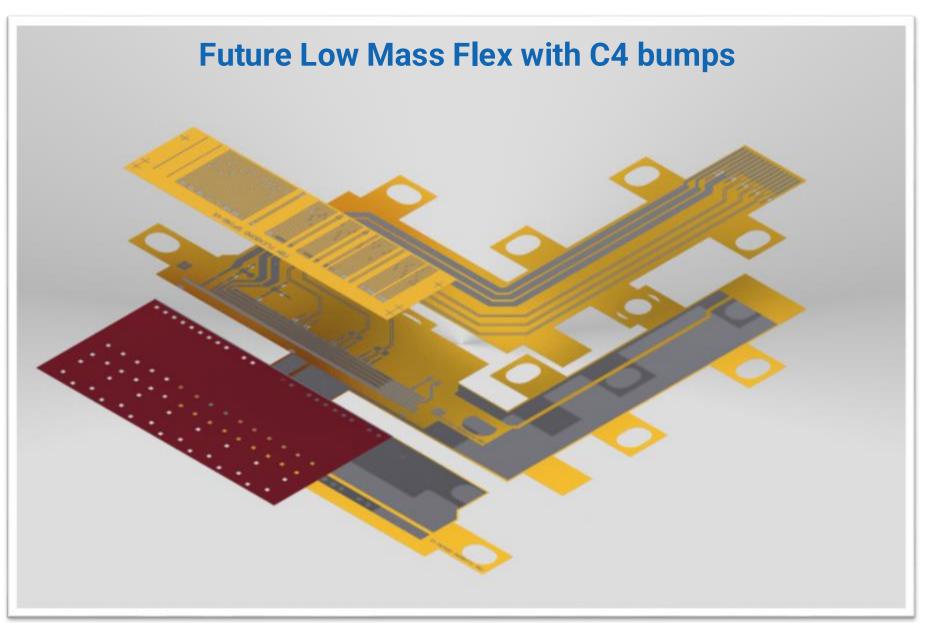

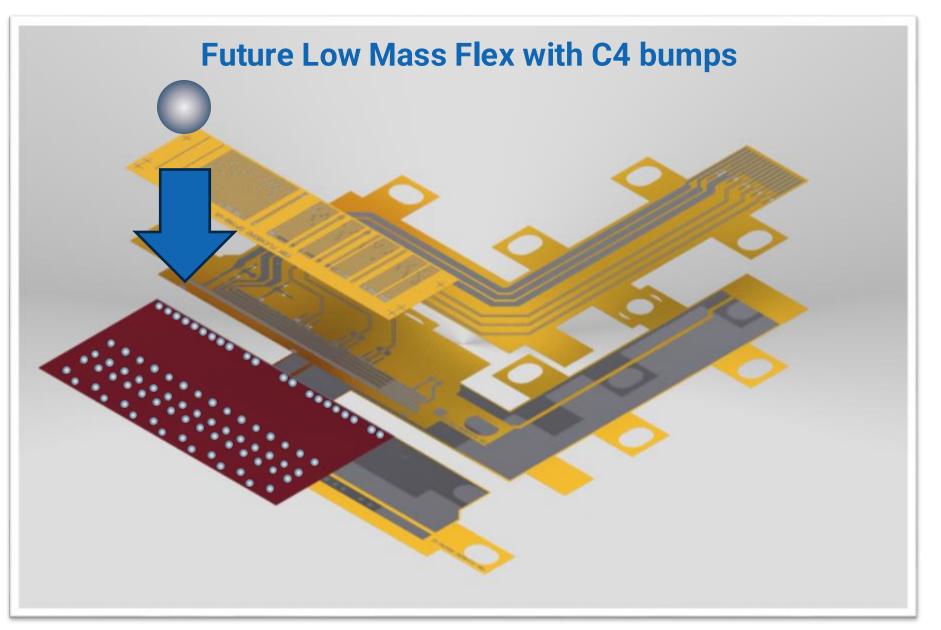

**Future Developments**

**Current Roadmap**

#### **Current Tech Roadmap priorities**

- Stacking

- Plating (Ni, ENIG)

- Space qualification

- Low X/X<sub>0</sub> Flip-Chip on Flex

- Signal integrity

- High data rates (few GHz)

- Multi-chip modules

**Future Developments**

**Current Roadmap**

#### **Current Tech Roadmap priorities**

- Stacking

- Plating (Ni, ENIG)

- Space qualification

- Low X/X<sub>0</sub> Flip-Chip on Flex

- Signal integrity

- High data rates (few GHz)

- Multi-chip modules

page 014

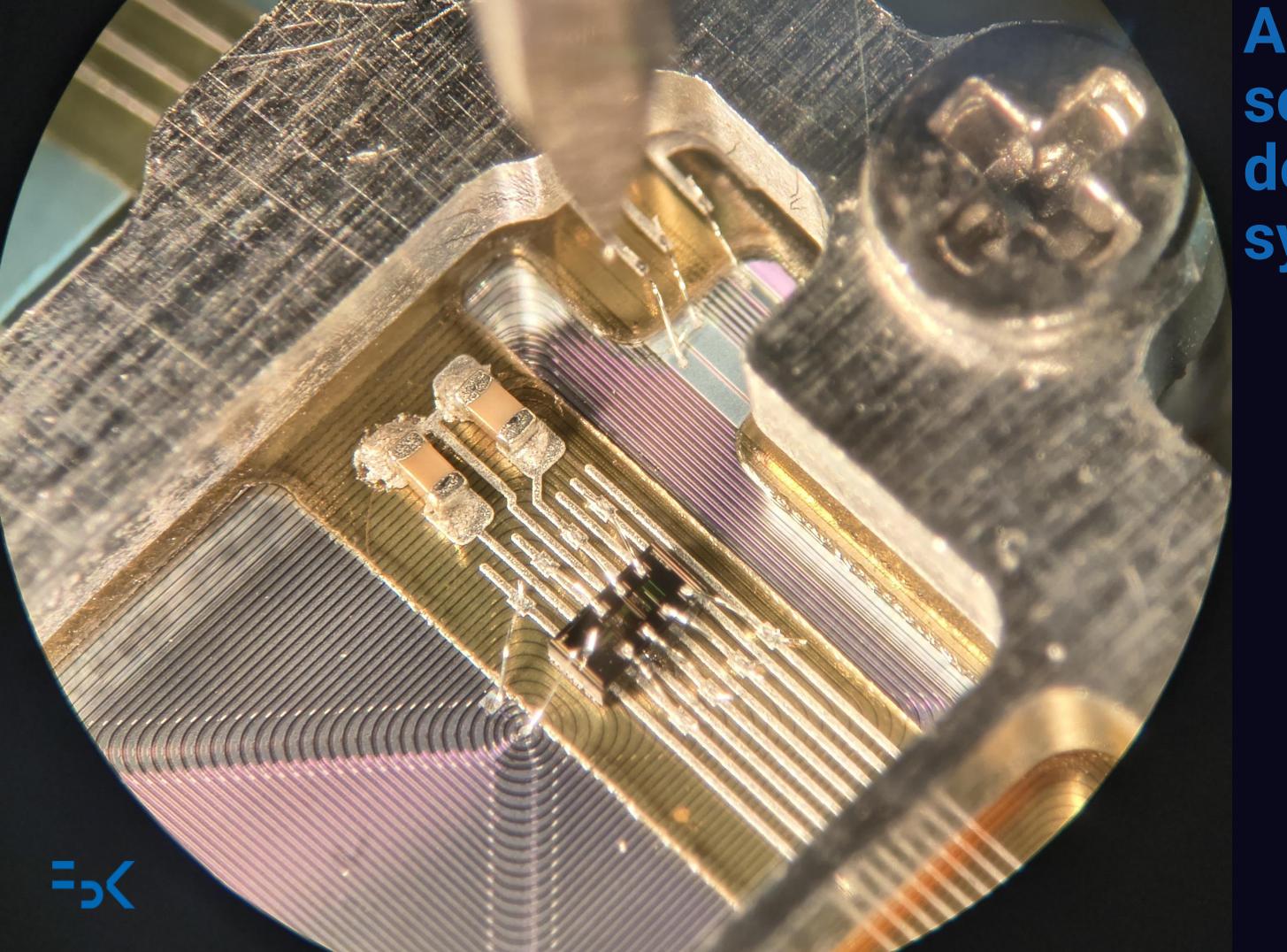

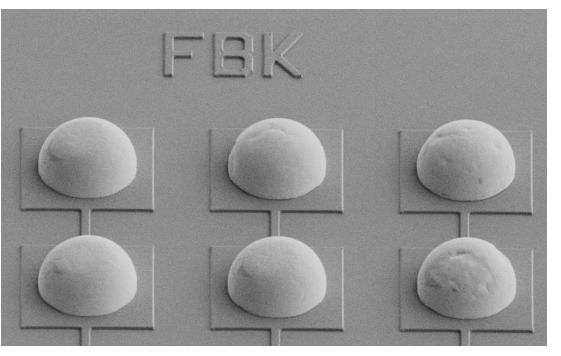

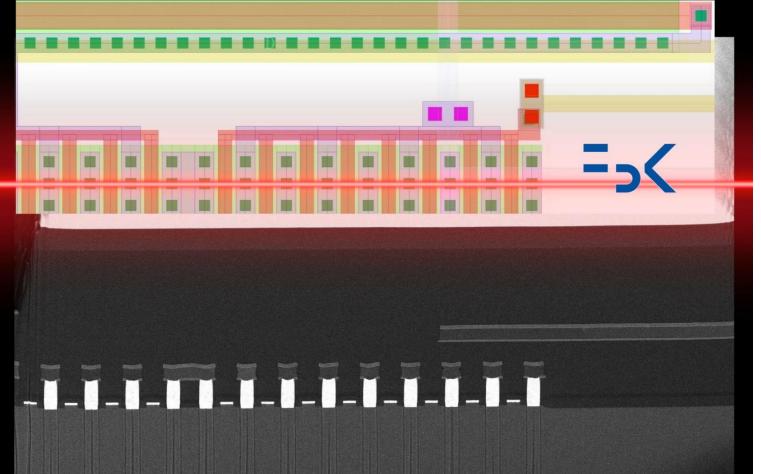

## FBK status update

<u>Anze</u> <u>Sitar</u>

Giovanni **Paternoster**  **David Novel**

Internal upgrades on

Evgeny **Demenev**

Fabio Acerbi

**Tiziano** Facchinelli

interconnection technologies

Giovanni Palù

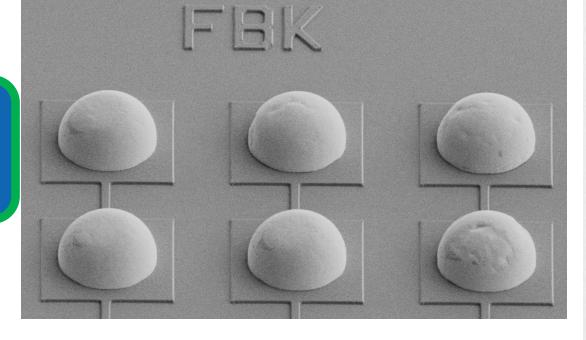

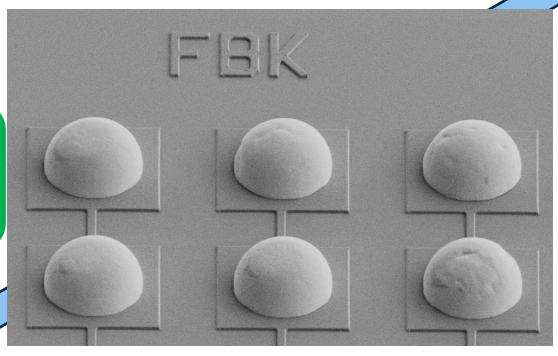

2.00 kV 0.10 nA SE

curr

mode det WD

ETD 4.4 mm 250 μm 2 000 ×

HFW

mag 🗆

100 μm-FBK Helios PFIB

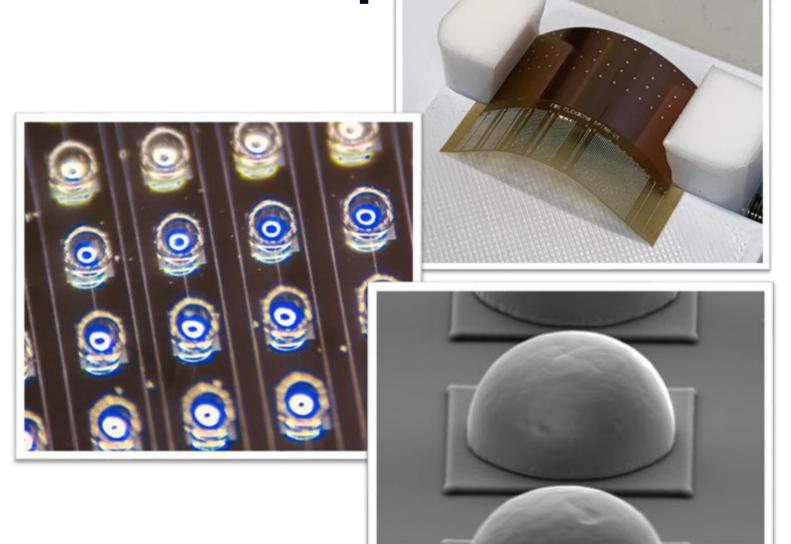

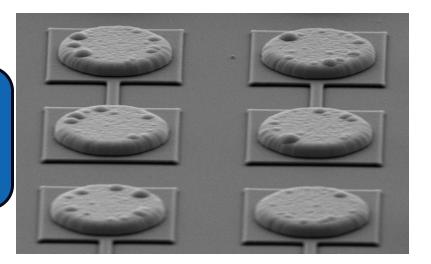

#### **FBK 3D integration**

#### **Current capabilities**

- 1. Sputtering system (various metal layers, under bump metal UBM)

- 2. Evaporators (various metal layers, under bump metal UBM)

- 3. Electrodeposition of Au

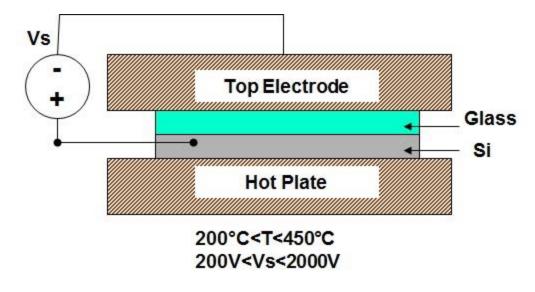

- 4. Anodic bonding of wafers

- 5. Adhesive bonding and debonding of wafers

- 6. Grinding & polishing down to micron thickness

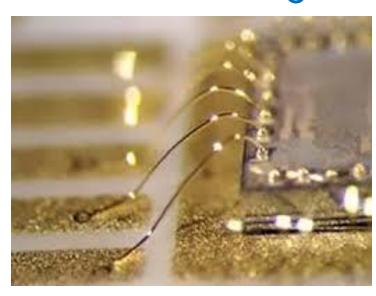

- 7. Semi-automatic Wirebonding

#### **Anodic bonding**

#### Wire bonding

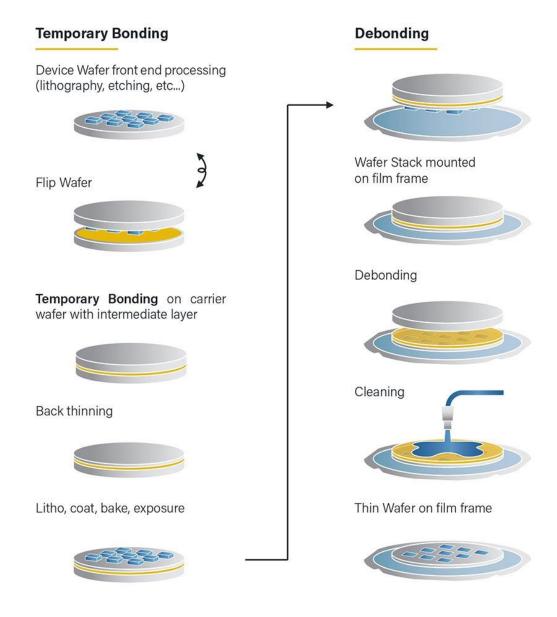

#### Temporary (de)bonding

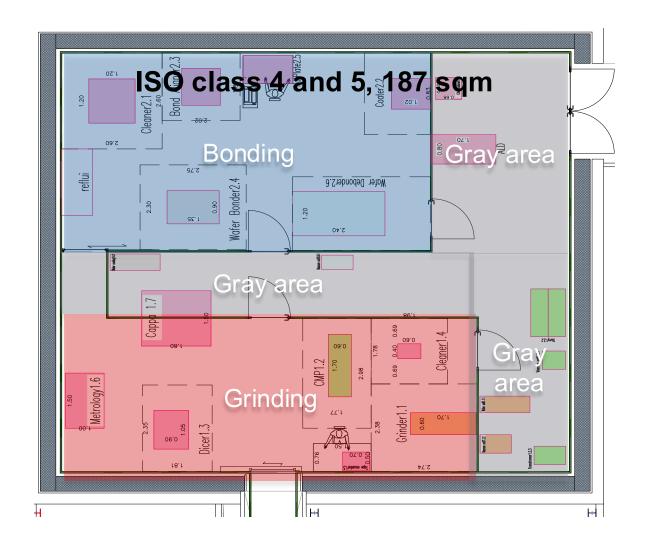

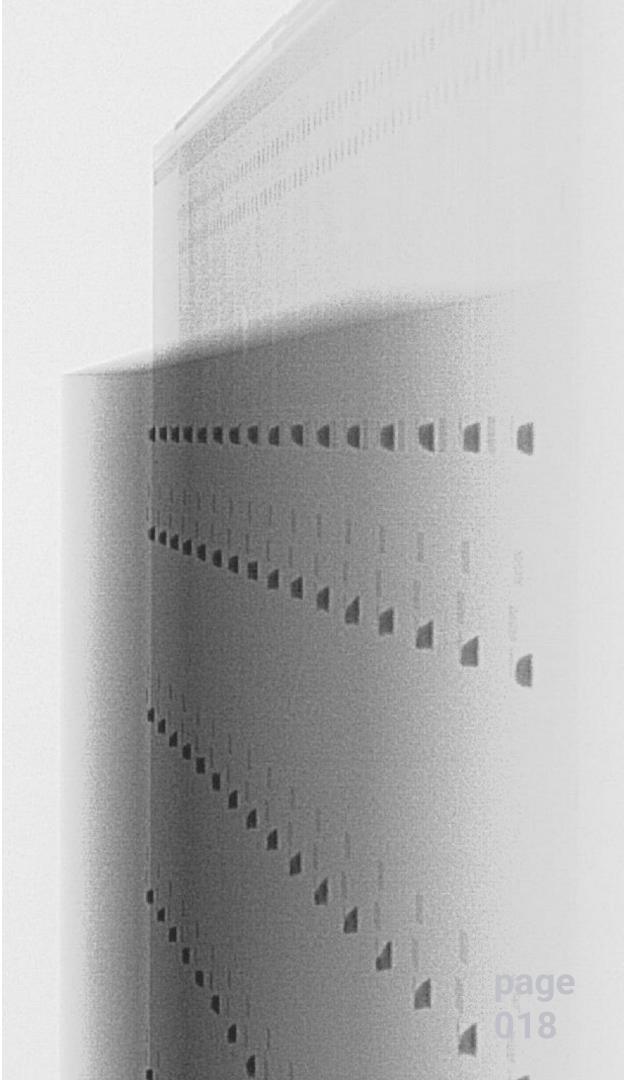

## FBK 3D integration New Cleanroom – operational

- Wafer Temporary Bonding/Debonding

- Metal and Fusion Direct Bonding

- Grinding and Polishing

- Metrology for 3D stacked wafers

- ALD

Pitch (> 70 μm) Chips, wafers, PCBs, Flex Electroless plating

UBM

Nickel, (Palladium), Gold

Pitch (> 70 μm) Chips, wafers, PCBs, Flex Electroless plating

UBM

Nickel, (Palladium), Gold

Chips, wafers, PCBs, Flex

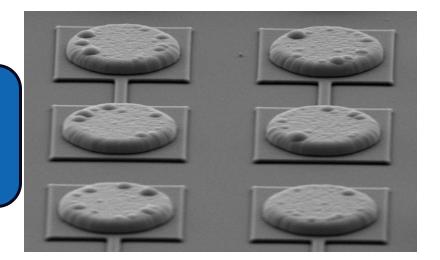

Solder ball deposition (30) 40-250 µm

Already installed in FBK

Pitch (> 70 μm) Chips, wafers, PCBs, Flex Electroless plating

UBM

Nickel, (Palladium), Gold

Chips, wafers, PCBs, Flex

Solder ball deposition (30) 40-250 µm

Already installed in FBK

Chip to chip Chip to wafer Chip to PCBs

Flip-Chip

Pitch (> 70 μm) Chips, wafers, PCBs, Flex Electroless plating

UBM

Nickel, (Palladium), Gold

Electroplating

UBM + Solder Cap

Copper, Nickel, Tin/Silver (+ Gold)

Fine Pitch (> 20 µm) Wafers only

Chips, wafers, PCBs, Flex

Solder ball deposition (30) 40-250 µm

Already installed in FBK

Flip-Chip

Chip to chip Chip to wafer Chip to PCBs

New installations are planned in FBK, starting from 2026

## 50 & DRD3

# HV-CMOS Pixel Detector Demonstrator with Serial Powering and Innovative Interconnections

3rd DRD3 Week on Solid State Detectors R&D Amsterdam, 2-6 June 2025

**Attilio Andreazza**

Yanyan Gao

Università di Milano and INFN

University of Edinburgh

**CCF Project Proposal** by

Birmingham, Bristol, Edinburgh, FBK, Heidelberg, Hochschule RheinMain, IHEP, KIT, Lancaster, Milano, Pisa, Torino, Trento

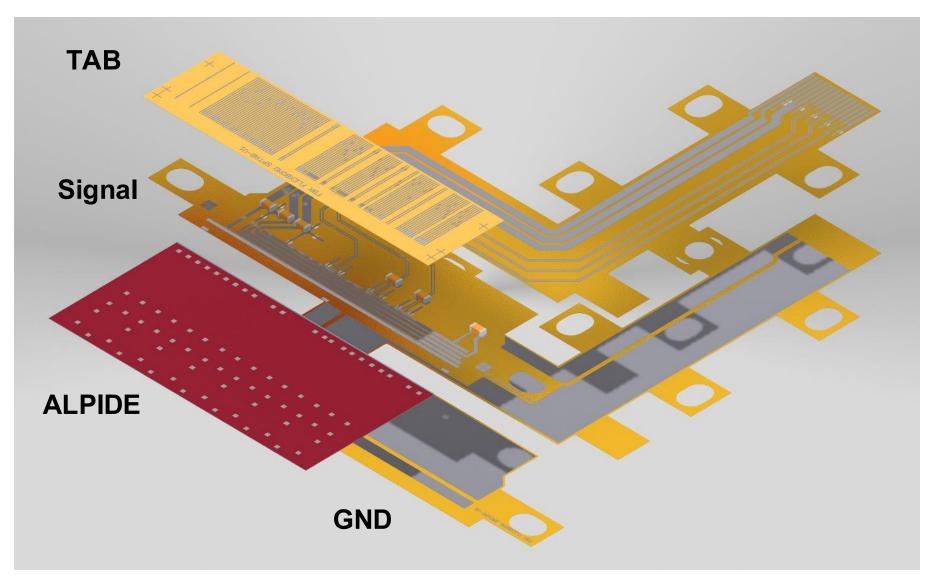

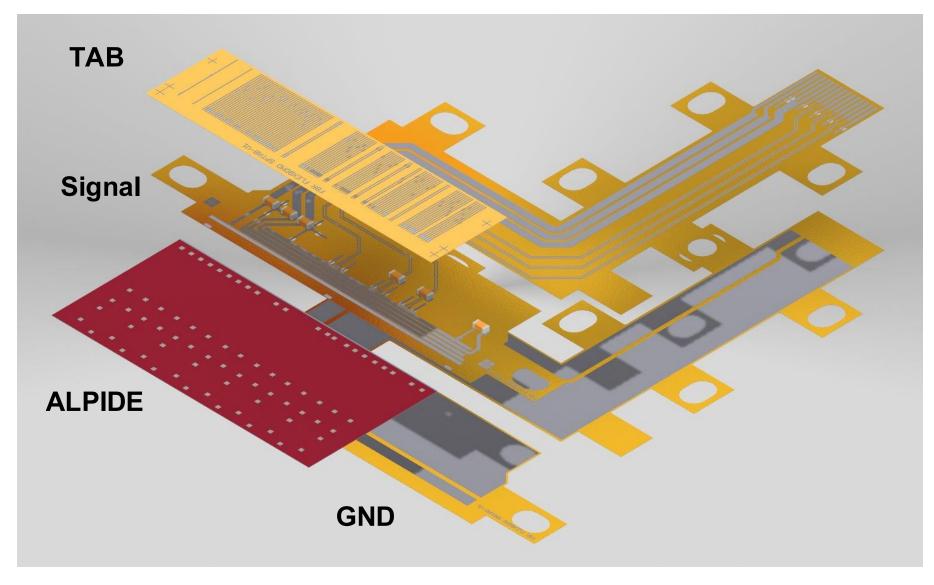

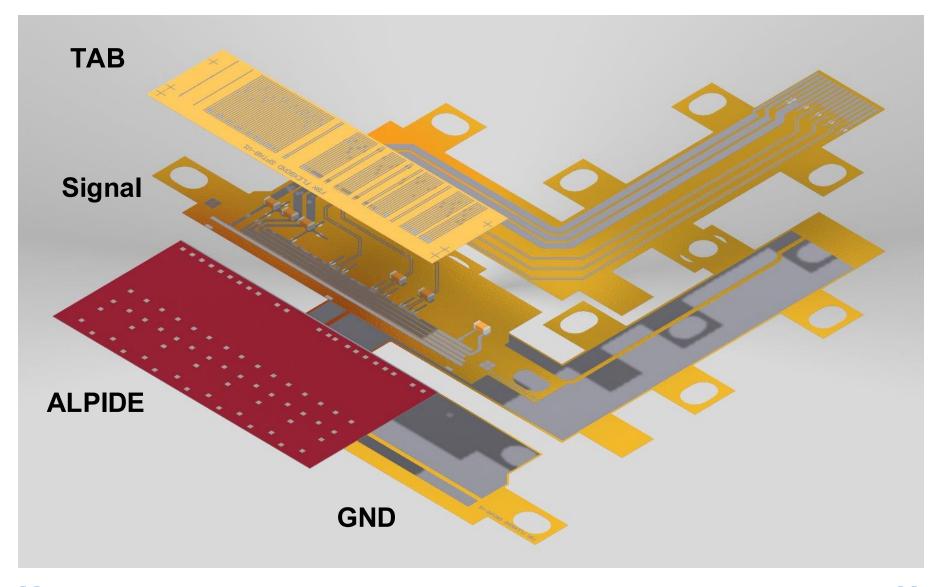

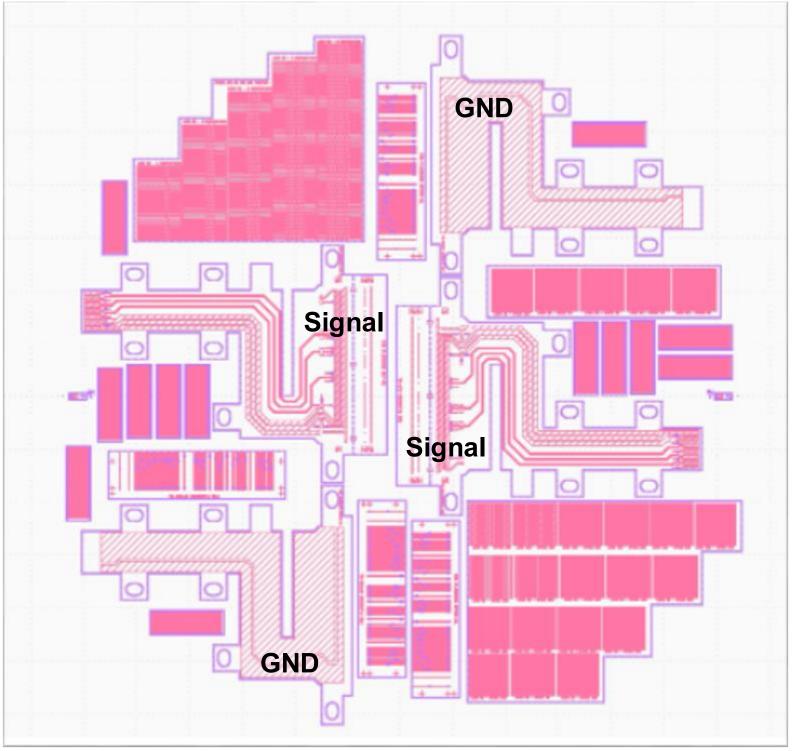

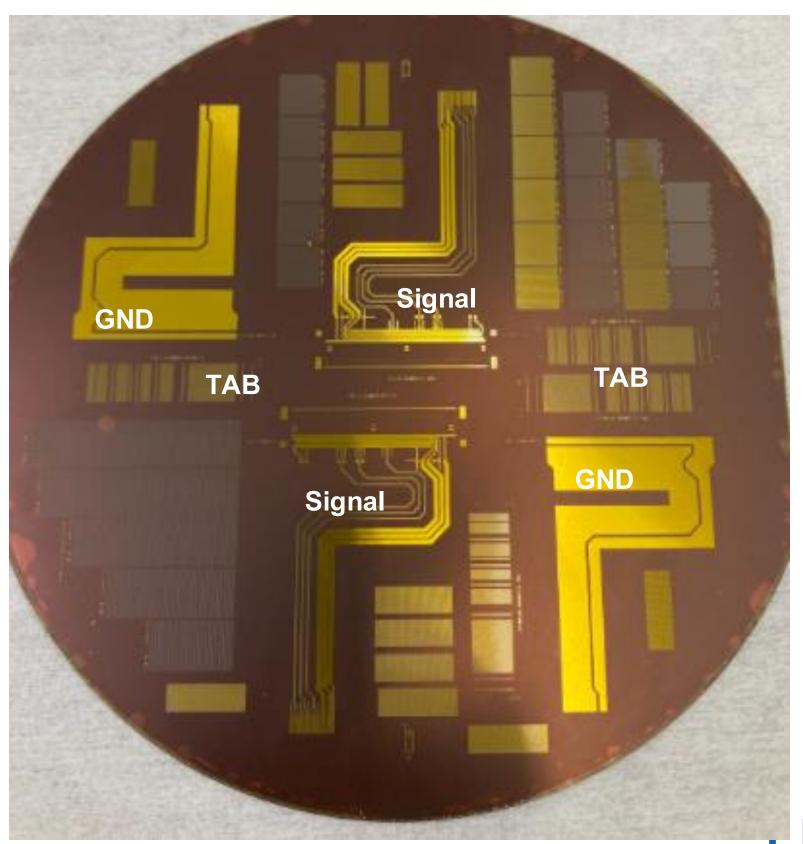

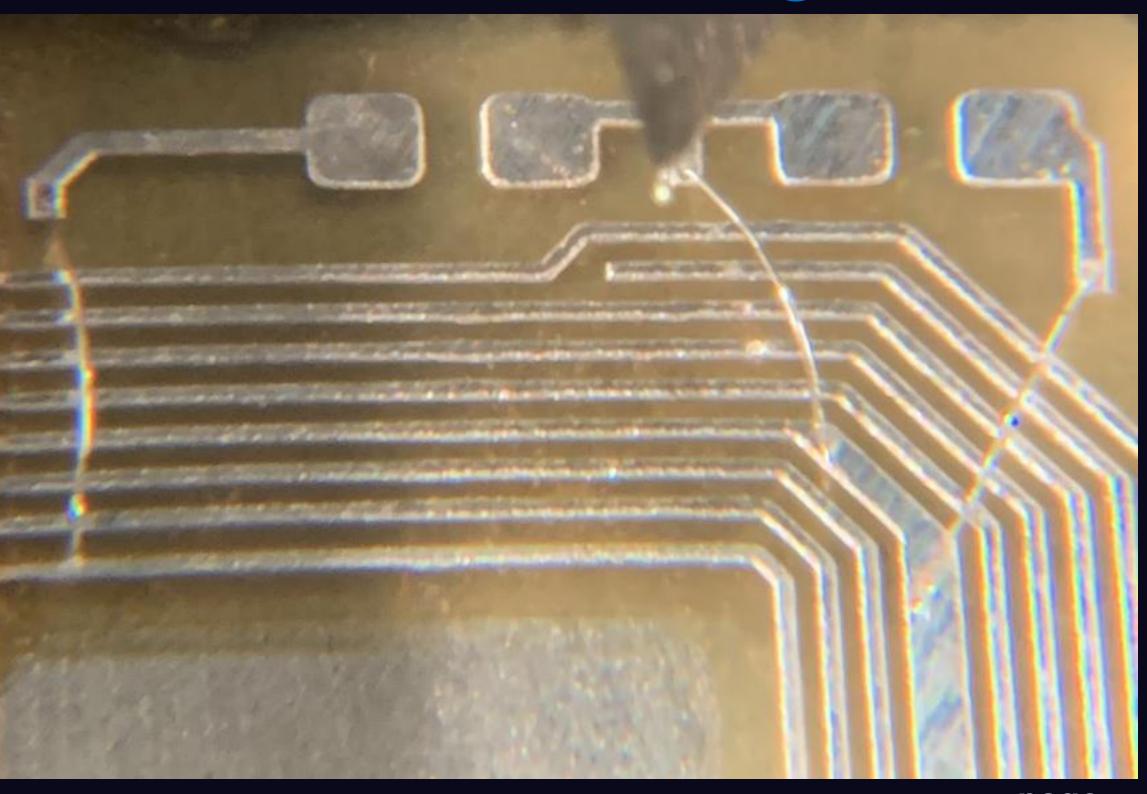

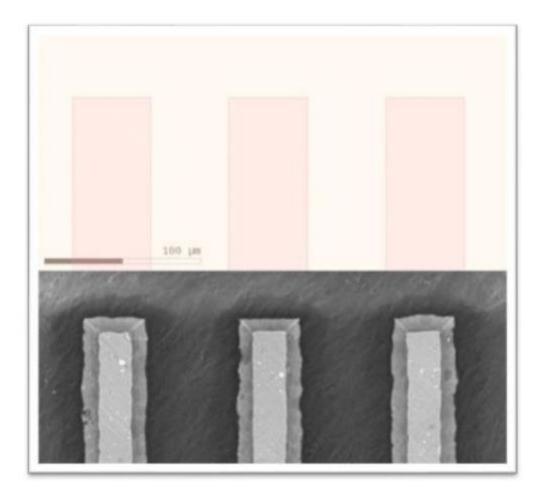

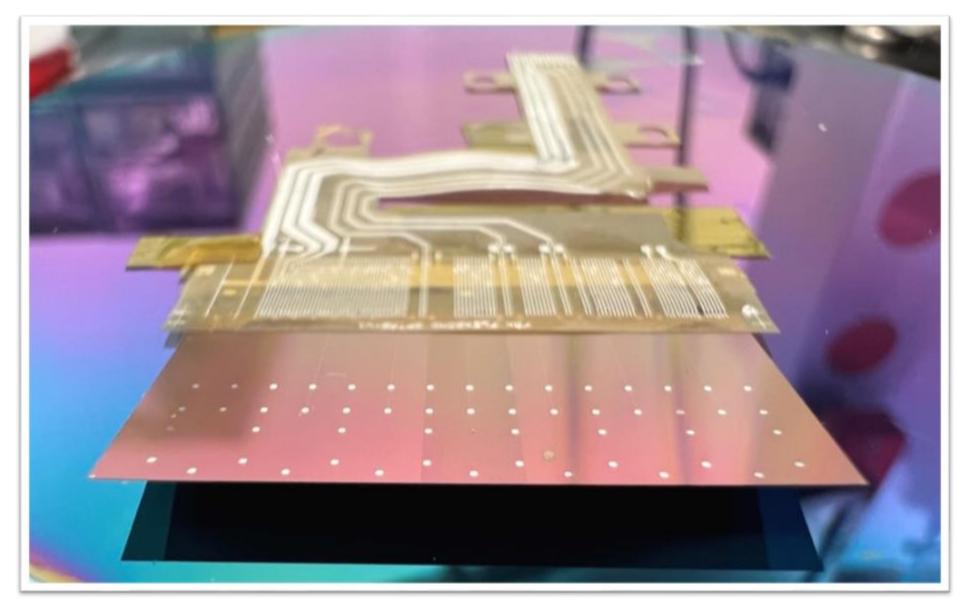

#### Stage 2: FBK technology DRD3

- Fabrication process inspired from the state-of-art LTU-Kharkiv [DOI: 10.15407/fm24.01.143]

- Processing inside FBK cleanrooms

- Kapton-Al PCBs

- 20 μm Al thickness

- 25 Kapton thickness

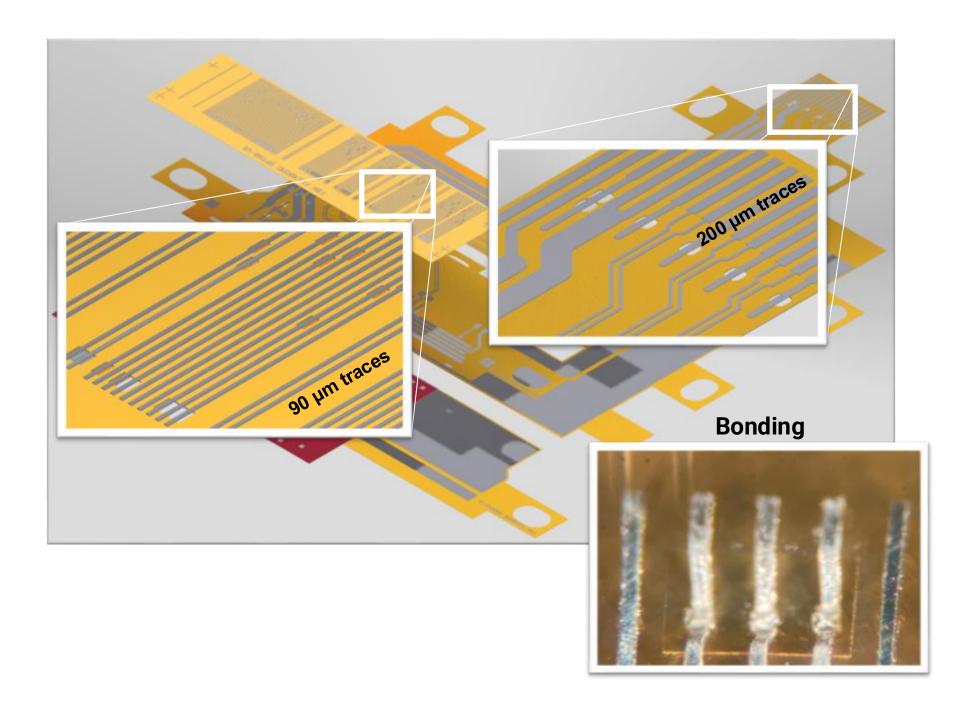

- Wafer level manufacturing (6" wafers)

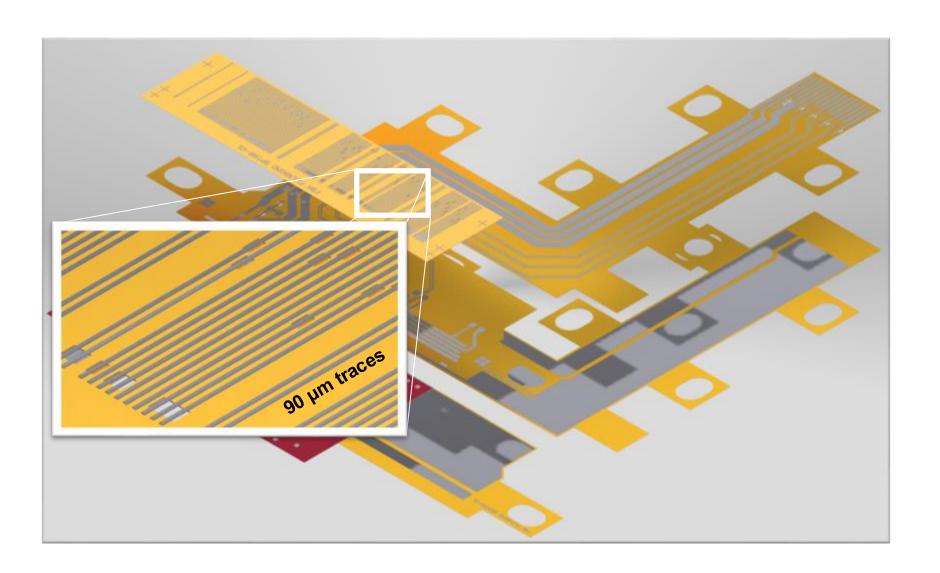

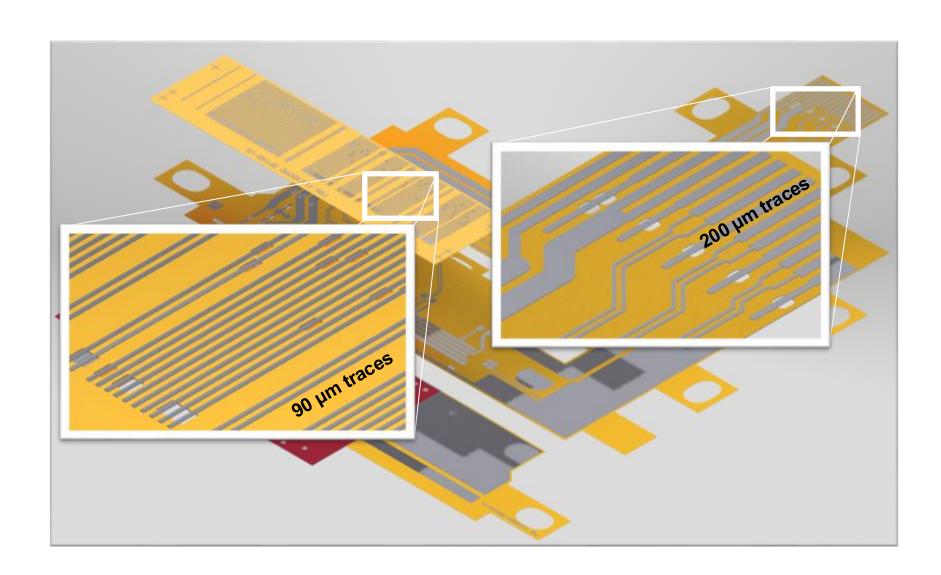

- Feature size

- minimal size is  $2 \times Al$  thickness =  $40 \mu m$

- very high line density (90 μm pitch)

- Interconnection

- spTAB 75  $\times$  75  $\mu$ m tool tip

- flex-to-chip TAB

- flex-to-flex TAB:

- use TAB as vias to reduce overall material

- connection to additional flexible PCB

3rd DRD3 week on solid state detectors R&D

**FBK contact: Maurizio Boscardin**

# In-house plating, hybridisation and module-integration technologies for pixel detectors

WG7 Interconnect Dominik Dannheim

LPNHE, CERN, FBK, UNIGE

PIRP

## Thank you!

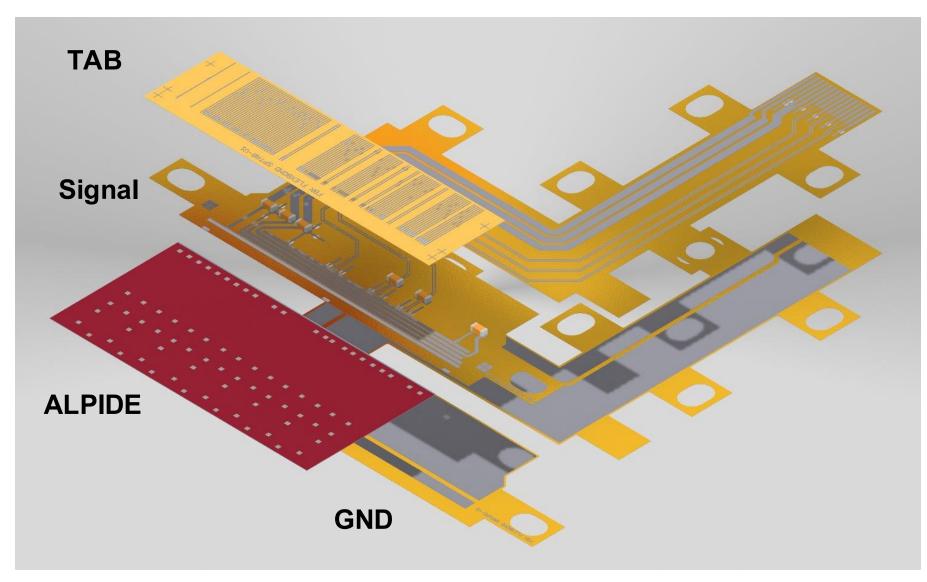

## Low mass Aluminium Flex Platform The recipe

50 μm ALPIDE chip + 90 μm Aluminium-Kapton flex PCB double layer

- ☐ Flex cable with Aluminium

- $(X_{OAI} = 8.9 \text{ cm}, X_{OCu} = 1.4 \text{ cm})$

- ☐ Minimal thickness

- 20 μm Al /layer

- 25 μm Kapton /layer

- 0.03% X/X0 /layer

- ☐ Tape Automated Bonding

- Single point Tape Automated Bonding (spTAB)

- Cross-imaged bonding tip

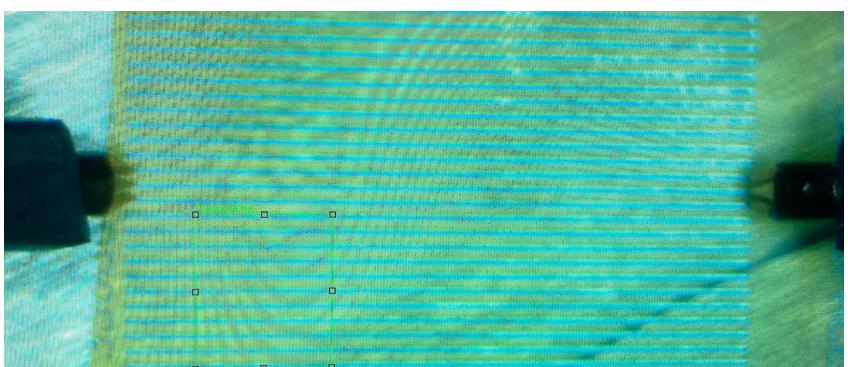

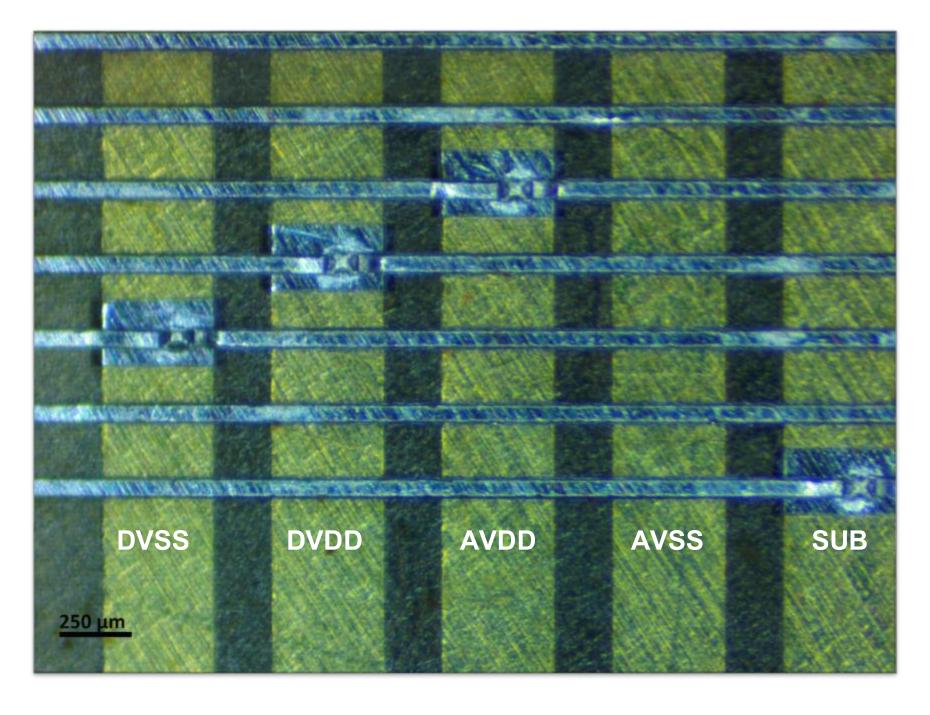

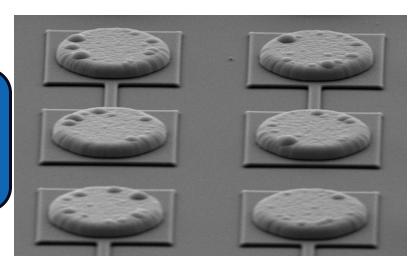

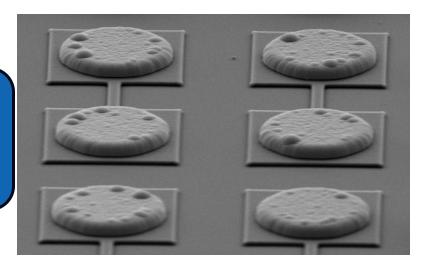

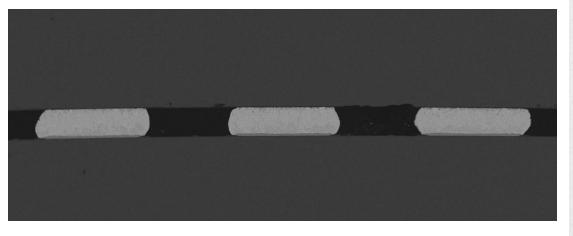

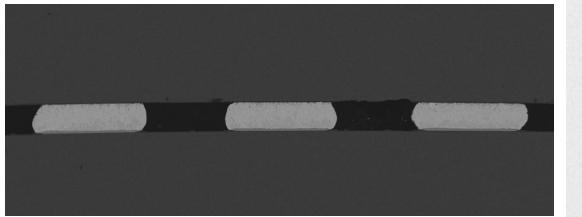

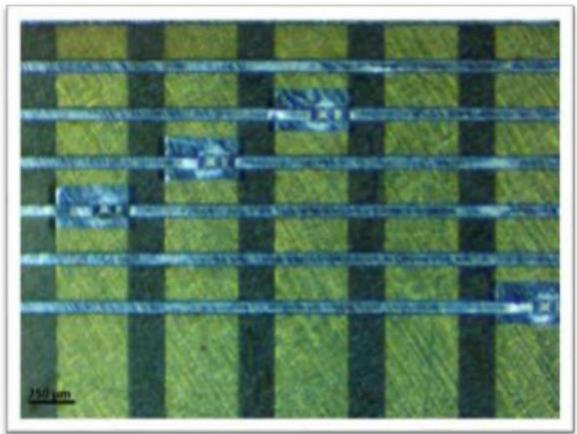

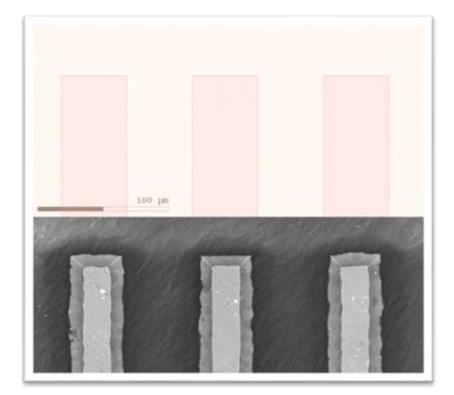

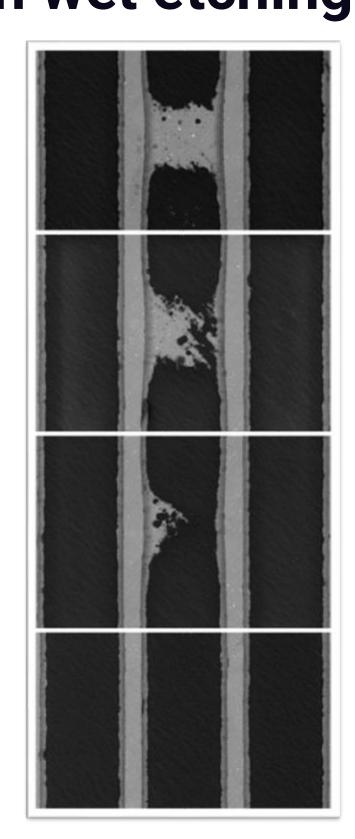

#### Low mass Aluminium Flex Platform Aluminium patterning with wet etching

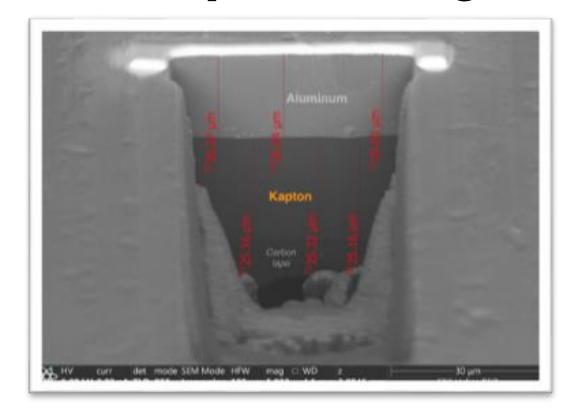

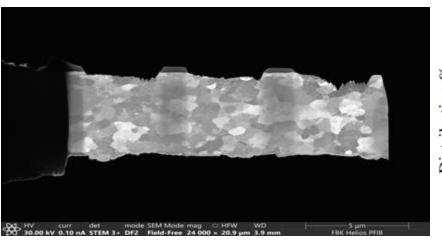

Cross section of the PI-aluminium (20-25 µm) substrate

Aluminium etching optimization

#### High patterning control

- Aluminium thickness of 20 μm is our standard

- Minimum trace width and spacing =  $40 \mu m$  for this aluminium thickness (can be decreased with thinner Aluminium)

| Thickness (µm) | Measured Resistivity ( $\mu\Omega$ cm) |

|----------------|----------------------------------------|

| 20             | 3.02                                   |

Preliminary measurements on resistivity of the aluminium

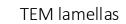

#### **Device & Material characterization**

**Examples**

MATERIALS

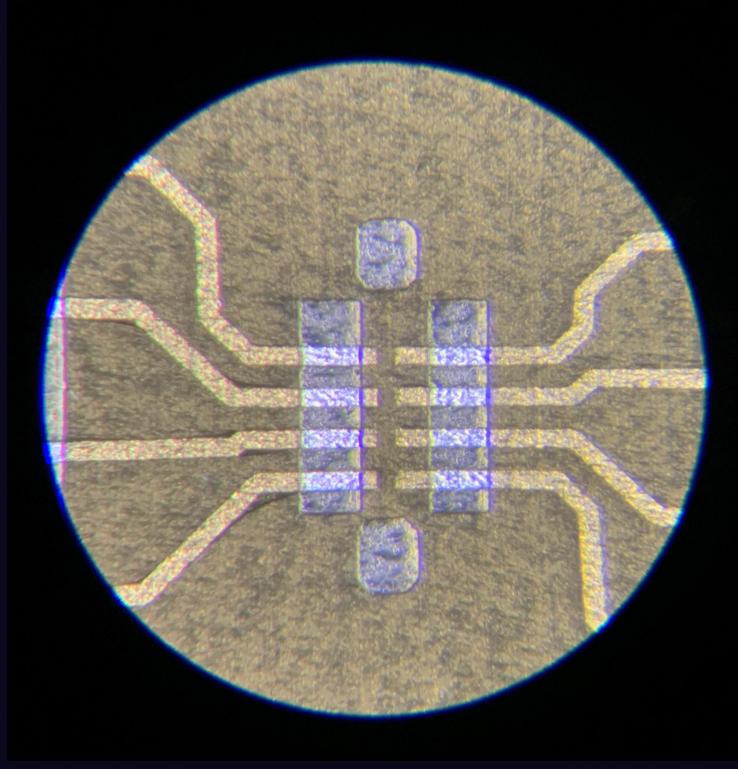

**Top view ASIC** layout

> **Lateral view Cross**section of the chip

Characterization of grain size and crystallographic orientation

ASIC defect correction

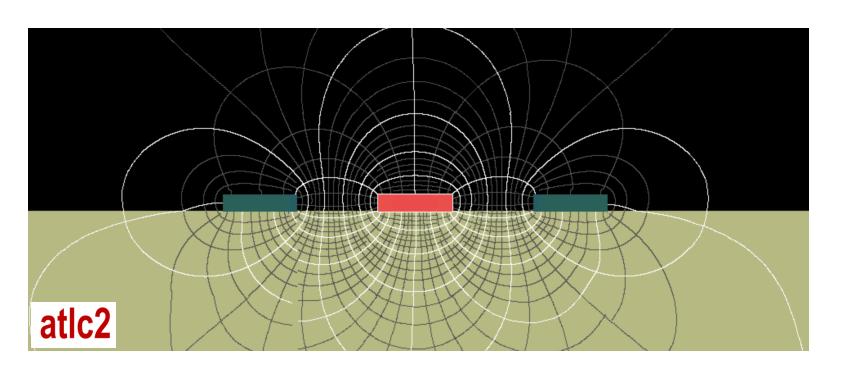

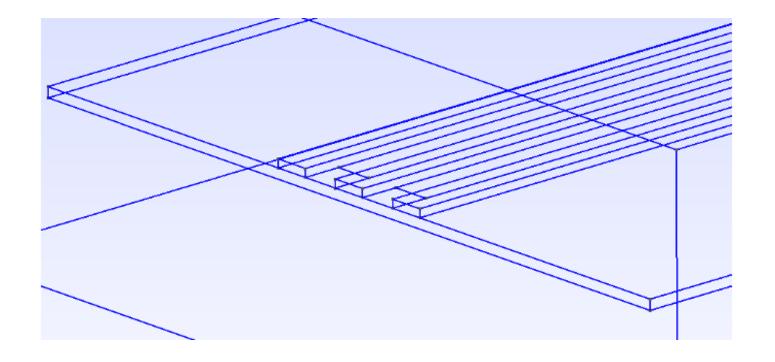

## Ongoing R&D FEM simulations

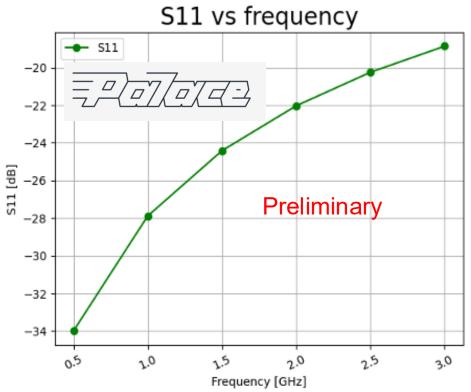

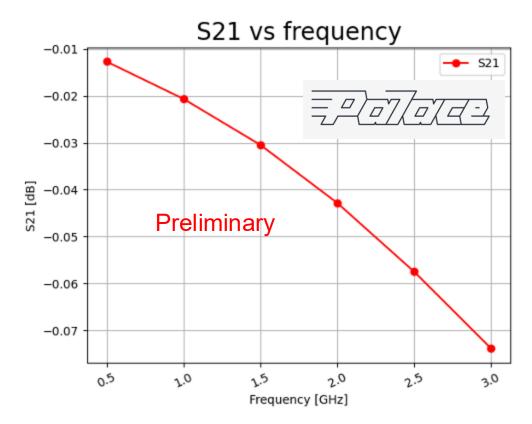

## Ongoing R&D VNA measurements