Intel Technologies

GridKa 2012 28 August 2012 Herbert Cornelius Intel

### Legal Disclaimer

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

All products, computer systems, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copyright © 2012, Intel Corporation. All rights reserved.

\*Other names and brands may be claimed as the property of others.

## Legal Disclaimers: Performance

- Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance of Intel

products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance. Buyers

should consult other sources of information to evaluate the performance of systems or components they are considering purchasing. For more

information on performance tests and on the performance of Intel products, Go to:

- Intel does not control or audit the design or implementation of third party benchmarks or Web sites referenced in this document. Intel encourages all of its customers to visit the referenced Web sites or others where similar performance benchmarks are reported and confirm whether the referenced benchmarks are accurate and reflect performance of systems available for purchase.

- Relative performance is calculated by assigning a baseline value of 1.0 to one benchmark result, and then dividing the actual benchmark result for the baseline platform into each of the specific benchmark results of each of the other platforms, and assigning them a relative performance number that correlates with the performance improvements reported.

- SPEC, SPECint, SPECfp, SPECrate. SPECpower, SPECjAppServer, SPECjEnterprise, SPECjbb, SPECompM, SPECompL, and SPEC MPI are trademarks of the Standard Performance Evaluation Corporation. See <u>http://www.spec.org</u> for more information.

- TPC Benchmark is a trademark of the Transaction Processing Council. See <u>http://www.tpc.org</u> for more information.

- SAP and SAP NetWeaver are the registered trademarks of SAP AG in Germany and in several other countries. See <u>http://www.sap.com/benchmark</u> for more information.

- INFORMATION IN THIS DOCUMENT IS PROVIDED "AS IS". NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO THIS INFORMATION INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

- Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance of Intel products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance. Buyers should consult other sources of information to evaluate the performance of systems or components they are considering purchasing. For more information on performance tests and on the performance of Intel products, reference www.intel.com/software/products.

### **Optimization Notice**

Intel<sup>®</sup> compilers, associated libraries and associated development tools may include or utilize options that optimize for instruction sets that are available in both Intel<sup>®</sup> and non-Intel microprocessors (for example SIMD instruction sets), but do not optimize equally for non-Intel microprocessors. In addition, certain compiler options for Intel compilers, including some that are not specific to Intel micro-architecture, are reserved for Intel microprocessors. For a detailed description of Intel compiler options, including the instruction sets and specific microprocessors they implicate, please refer to the "Intel<sup>®</sup> Compiler User and Reference Guides" under "Compiler Options." Many library routines that are part of Intel<sup>®</sup> compiler products are more highly optimized for Intel microprocessors than for other microprocessors. While the compilers and libraries in Intel<sup>®</sup> compiler products offer optimizations for both Intel and Intel-compatible microprocessors, depending on the options you select, your code and other factors, you likely will get extra performance on Intel microprocessors.

Intel<sup>®</sup> compilers, associated libraries and associated development tools may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include Intel<sup>®</sup> Streaming SIMD Extensions 2 (Intel<sup>®</sup> SSE2), Intel<sup>®</sup> Streaming SIMD Extensions 3 (Intel<sup>®</sup> SSE3), and Supplemental Streaming SIMD Extensions 3 (Intel<sup>®</sup> SSE3) instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors.

While Intel believes our compilers and libraries are excellent choices to assist in obtaining the best performance on Intel<sup>®</sup> and non-Intel microprocessors, Intel recommends that you evaluate other compilers and libraries to determine which best meet your requirements. We hope to win your business by striving to offer the best performance of any compiler or library; please let us know if you find we do not. Notice revision #20101101

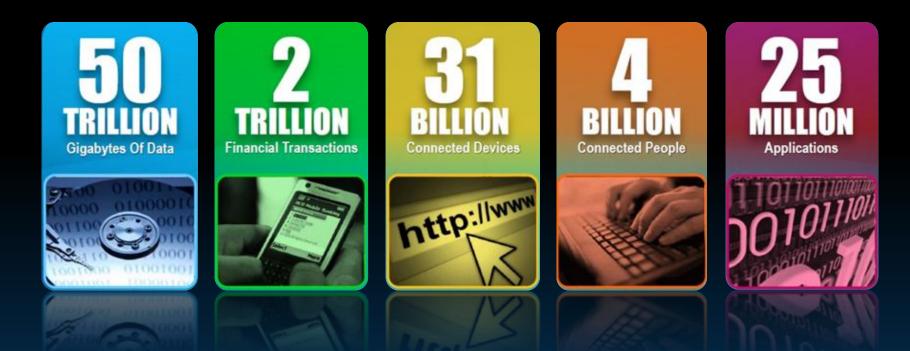

# **COMPUTING 2020**

(Source: IDC Directions 2010, March 2010, ICT Outlook forecast)

5

## Intel's Approach to Cloud Solutions

### Define and Prioritize Cloud Requirements

### Intel Building Blocks to Address Requirements

### Complete Partner Solutions

| 1997 | 1 TFLOPS                                 | \$55,000 / GFLOPS                     |

|------|------------------------------------------|---------------------------------------|

| 2009 | >500 TFLOPS                              | <\$100 / GFLOPS                       |

| 2009 | >500 TFLOFS<br>>500x<br>more performance | <\$1007 GFLOPS<br>>550x<br>less costs |

INTEL 28.08.2012

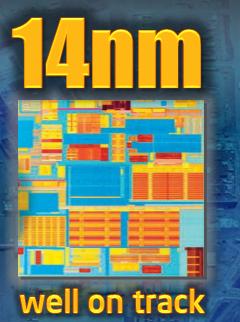

22 nm

2011

32 nm

2009

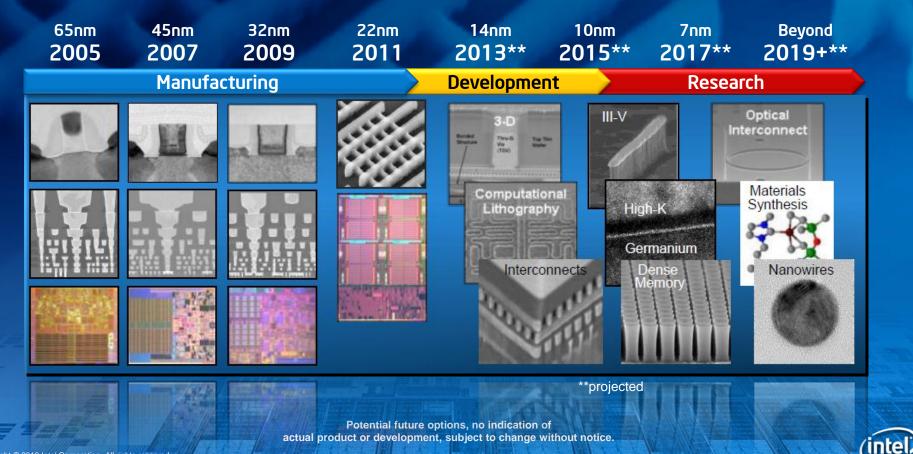

### Predictable Silicon Track Record Executing to Moore's Law

65 nm

2005

90 nm

2003

Enabling new devices with higher functionality & complexity while controlling power, cost, and size

45 nm

2007

180 nm

130 nm

200

### **Process Technology Research @ Intel**

### **Computing Trends and Design Points**

## Just Arrived ...

# THE UNBELIEVABLY FAST X900 with Intel Inside

### MYTH:

Energy Efficient Performance can only be achieved with (very) Special architected Hardware, Software and Tools

1997: THE FIRST INTEL® TERAFLOP COMPUTER

consisted of:

and occupied:

9,298 INTEL

72 SERVER

9,298 PROCESSORS

72 CABINETS

THE INTEL® XEON® PHI™ COPROCESSOR

will provide:

1 TERAFLOP OF

PERFORMANCE

INTEL - ASPERA 2012 15

Energy Effort Ferfortunce can only boochieved with (very) Stochieved with Hardwood Software and Tools

MYT

## **Intel in High-Performance Computing**

### A long term commitment to the HPC market segment

## Intel Technology is Changing HPC

Performance, Energy Efficiency, Reliability, TCO

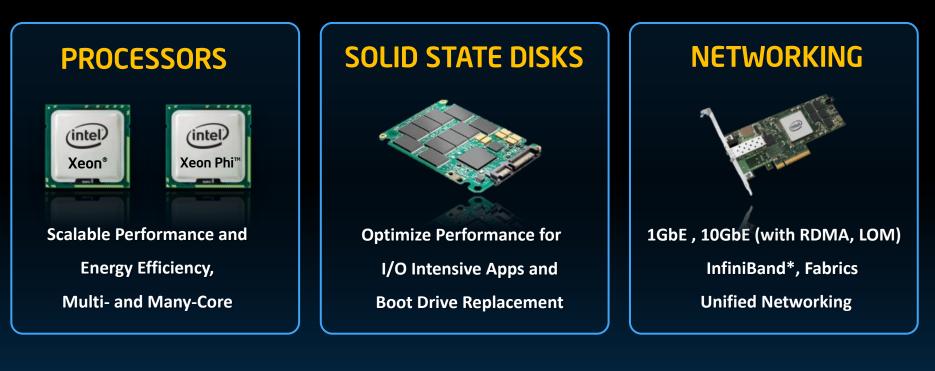

### A platform approach to high performance

Copyright © 2012 Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners [picture sizes not to scale and for illustration only]

### What's Intel Doing in 2012 in HPC ...

Intel<sup>®</sup> Xeon<sup>®</sup> Processor: E5-2600/4600 Product Families

### Intel<sup>®</sup> Many Integrated Core Architecture

### Fabric Technologies:

Cray's Aries Interconnect, Qlogic's TrueScale Product Family

### Intel<sup>®</sup> Software Development Tools

### **Intel Fabrics Environment**

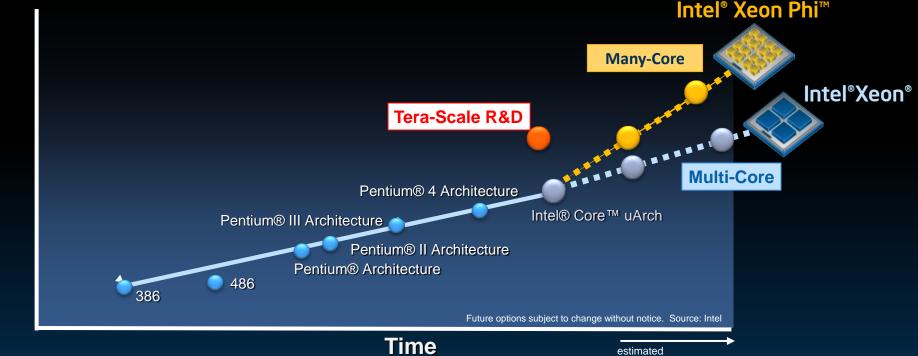

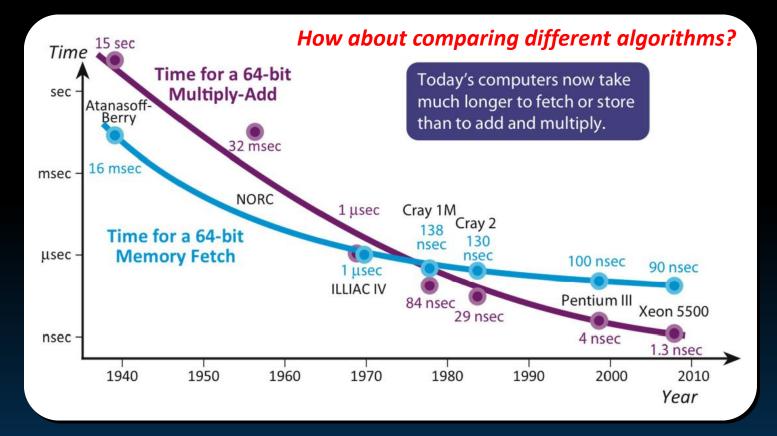

## **Increasing Processor Performance**

Through Many-Core Technologies for Highly Parallel Workloads

### **FLOPS/Processor**

For illustration only. All dates, product descriptions, features, availability, and plans are forecasts and subject to change without notice.

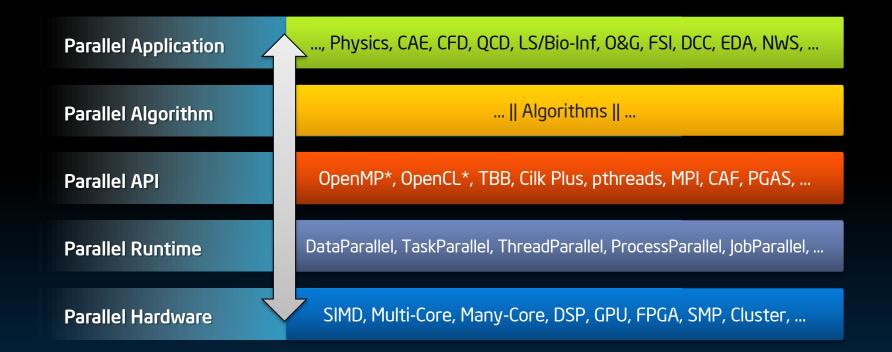

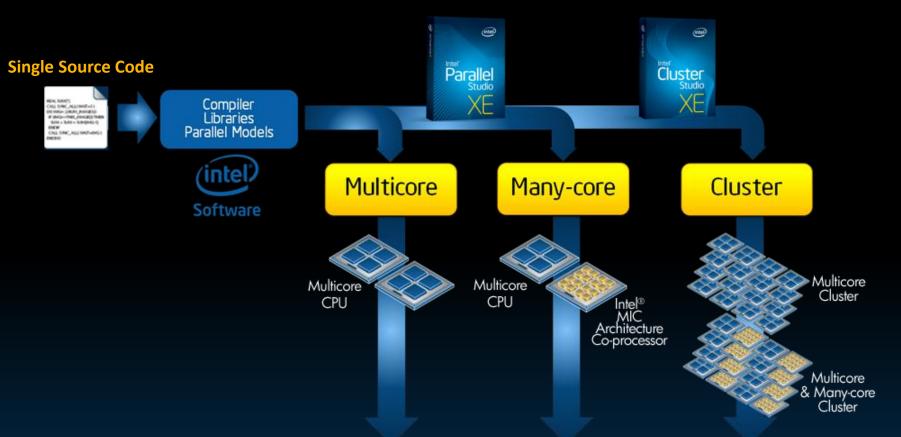

### **Parallel Computing & Programing**

Foundation of HPC Performance Suited for full scope of workloads with balanced architecture

Industry leading performance and performance/watt for serial & parallel workloads

Focus on fast single core/thread performance utilizing Multi-Core architectures

Performance and performance/watt optimized for highly parallelized compute intensive workloads

Common software tools with Xeon enabling efficient application readiness and performance tuning

x86/IA extension to Many-Core complementing Intel® Xeon®

Lots of cores/threads with wide SIMD

### C/C++, FORTRAN, ...

### OpenMP, MPI, ...

#### Same Comprehensive Set of SW Tools

Application Source Code Builds with a Compiler Switch

#### **Established HPC Operating System**

Offload and Native Autonomous Linux\* Node

### **Eliminate Need for Dual Programming Software Architecture**

Copyright © 2012 Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners For illustration only, potential future options subject to change without notice.

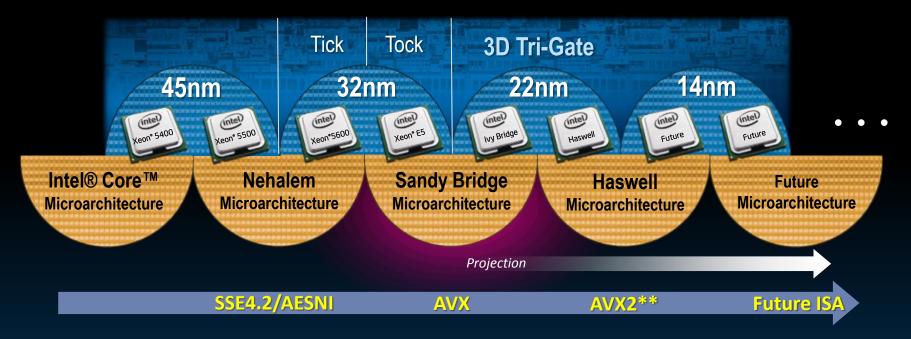

## **Tick-Tock Development Cycles**

Integrate. Innovate.

\*\*Intel® Architecture Instruction Set Extensions Programming Reference, #319433-012A, FEBRUARY 2012

Potential future options, subject to change without notice.

### Intel<sup>®</sup> Xeon<sup>®</sup> E5-2600 Series Processors

Best combination of high performance and energy efficiency – optimizes HPC & Cloud Solutions

Up to 8 Cores (16 Threads w/ HT) AVX 256-bit SIMD Instructions Up to 3.3GHz marked frequency Turbo-Technology 2 Up to 20MB shared Cache keon<sup>®</sup> VGOU Powerful. Intelligent.

[data are per processor]

Virtualization (VT) Trusted Execution (TXT) AES New Instructions Integrated PCI Express\* 3.0 (x40) Network Data Direct I/O (DDIO)

4 DDR3 Memory-Channel (up to 1600MHz) Up to 768GB memory Intelligent Power Management

### **Continued Processor Technologies**

General Purpose programmable and balanced

SIMD Processing continues as it is quite energy efficient

Multi/Many-Core with even more Threads

### Fast and Efficient shared Cache/Memory Hierarchy

Potential future options and features are projections and targets, subject to change without notice.

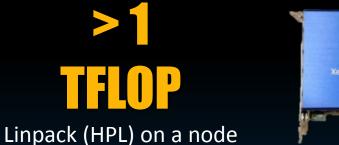

#### SC'11 November 2011

1 TFLOPS DP-F.P.

> (Early Silicon Architecture Demonstration)

# **MIC: Knights Corner**

- In 22nm process technology

- >50 cores/die energy efficient

- 512 bit SIMD instructions

- Prototype Si delivers 1TFLOPS sustained on DGEMM as architecture capability demonstration

- Runs Linux

- Can be

- a **<u>native network node</u>** (IP addressable, ssh in ...)

- used as an offload co-processor

- Common x86 programming models, techniques and tools

- Targeted by Intel compilers and SW-tools

- 3<sup>rd</sup> party software being enabled

## Intel<sup>®</sup> Xeon Phi<sup>™</sup> Product Family

based on Intel<sup>®</sup> Many Integrated Core Architecture

#### Many Cores compared to Multi-Core

Many smaller lower power Intel processor cores

Wider vector processing units for greater (generally) floating point performance/watt

#### **Highly Parallel**

Higher aggregate performance\*\*

Supports Data Parallel, Thread Parallel, Process/Task Parallel

Higher memory bandwidth\*\*

#### **Highly Programmable**

Standards-based: C/C++/FORTRAN

Abstract: no requirement to program to the underlying hardware

More than an accelerator: fully addressable, independent node in a cluster

Full support by Intel® Parallel Studio XE and Intel® Cluster Studio XE

### It's a Coprocessor, not an Accelerator

\*\*Relative to multi-core Intel Xeon processors.

## Intel<sup>®</sup> Xeon Phi<sup>™</sup> Product Family

based on Intel<sup>®</sup> Many Integrated Core Architecture

#### **Optimized, Highly Parallel**

Intel<sup>®</sup> Xeon Phi<sup>™</sup> **coprocessor** (pairs with Intel<sup>®</sup> Xeon<sup>®</sup> processor host via PCIe)

#### **Runs Complete Applications**

IP Addressable Open Source Linux OS Common Source Code Standard models of clustering

#### **Builds on / Advances**

State of the Art in Parallelism Intel Software Developer tools

### SMP on a chip!

Future "Knights"

Products

nights Corner

## The "Knights" Family

### "Knights Corner"

1<sup>st</sup> Intel<sup>®</sup> MIC architecture based product 22nm process >50 Intel Architecture cores TFLOPS of Performance Energy Efficient Offload Co-Processor and Native Linux\* Node Programming

"Knights Ferry"

Development Platform

### "Programmed like a computer"

All dates, product descriptions, availability, and plans are preliminary forecasts and subject to change without notice.

## Early Performance on Intel<sup>®</sup> Xeon Phi<sup>™</sup> Coprocessor

(Codenamed Knights Corner)

Small cluster with Intel<sup>®</sup> Xeon<sup>®</sup> E5 processor based nodes with early Intel<sup>®</sup> Xeon Phi<sup>™</sup> coprocessors

### In Production in 2012, Enabled by 22nm 3-D TriGate Transistors

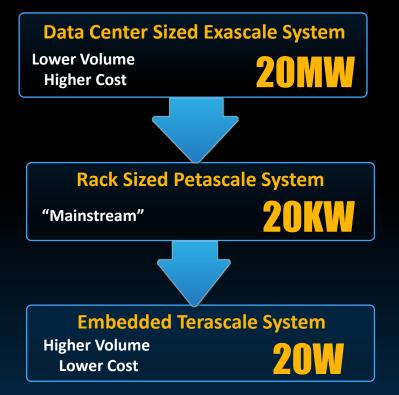

# Journey to **Exascale**

## Assume Exascale Computing at 20MW ...

#### **New Forms of Energy**

#### **Space Exploration**

#### **Ecological Sustainability**

**Medical Innovation**

#### And many others ....

## **HPC:** The Path to Exascale

Processors Intel<sup>®</sup> Xeon<sup>®</sup> Processor

#### Co-Processor Intel<sup>®</sup> Many Integrated Core

Scalability

### Software

## HPC: The Path to Exascale (cont.)

## "The Memory Wall"

### "ExtremeScale"

### August 6, 2010

The Defense Advanced Research Projects Agency (DARPA\*) has initiated the Ubiquitous High Performance Computing (UHPC) program to create an innovative, revolutionary new generation of computing systems that overcomes the limitations of current evolutionary approach. The goal of DARPA's UHPC program is to re-invent computing. It plans to develop radically new computer architectures and programming models that are **100 to 1,000 times more energy efficient, with higher performance, and that are easier to program than current systems.**

Prototype UHPC systems are expected to be complete by **2018**. UHPC systems will need to deliver a petaflop of High Performance Linpack (HPL) in a single cabinet and achieve an energy efficiency of at least **50 gigaflops/watt**.

**Intel** [and others] and the Defense Advanced Research Projects Agency (DARPA) have entered into a collaborative research agreement to investigate revolutionary hardware and software technologies for extreme-scale computing systems.

e.g. using Near Threshold Voltage research IA processor (IDF Fall 2011)

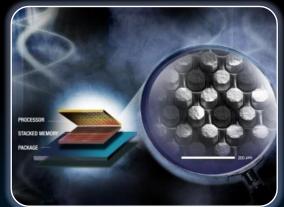

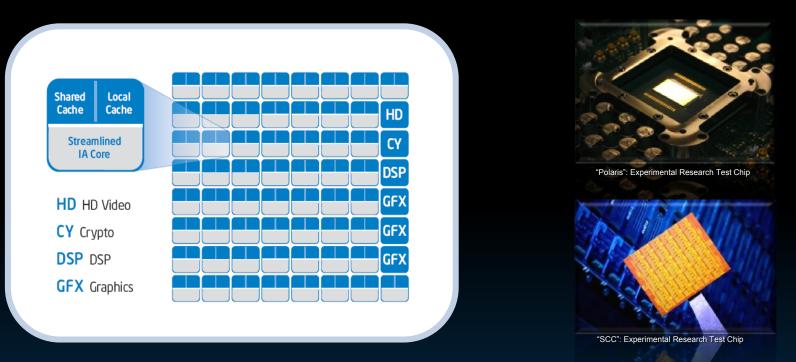

### Intel TeraScale Research Areas

### MANY-CORE COMPUTING

### **Teraflops** of computing power

### 3D STACKED MEMORY

### Terabytes of memory bandwidth

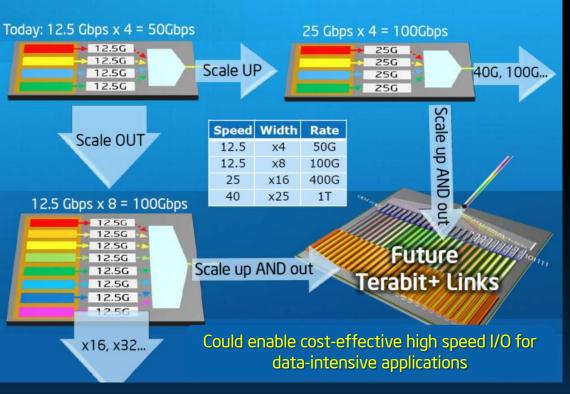

## SILICON Photonics

### **Terabits** of I/O throughput

Future vision, does not represent real products.

### Many-Core Chip Research

Future tera-scale chips could use an array of tens to hundreds of cores with reconfigurable caches, as well as special-purpose hardware accelerators utilizing a scalable on-die interconnect fabric.

Potential future options, no indication of actual product or development, subject to change without notice.

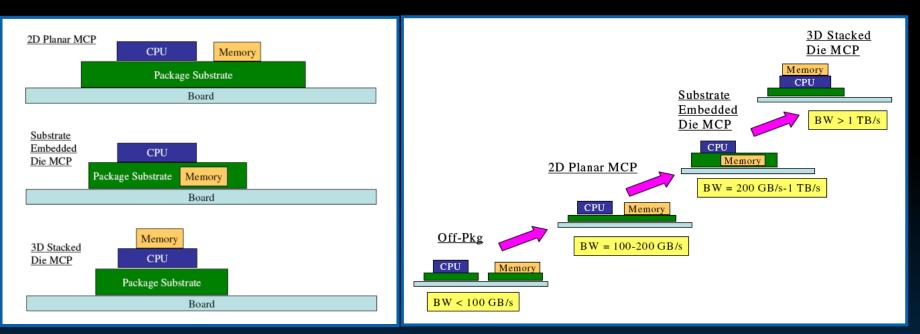

### Memory and CPU Package Architectures for addressing Bandwidth Challenges - Research

Package Technology to Address the Memory Bandwidth Challenge for Tera-scale Computing, Intel Technology Journal, Volume 11, Issue 3, 2007

Potential future options, no indication of actual product or development, subject to change without notice.

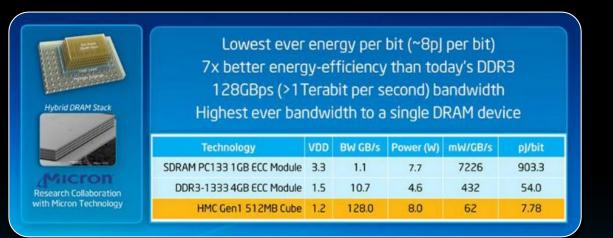

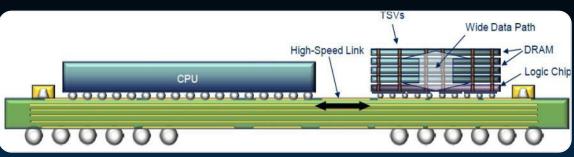

## Hybrid Memory Cube: Experimental DRAM

Highest Performance and most Energy Efficient DRAM in the Industry

http://www.micron.com/innovations/hmc.html

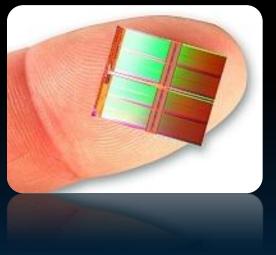

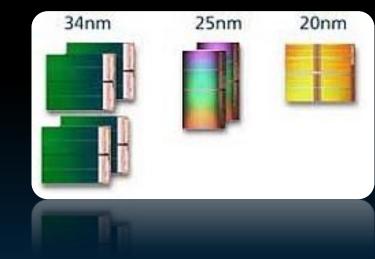

## **Intel and Micron's Joint-Development Venture**

IM Flash Technologies (IMFT)

### 128 Gbit (16GB) NAND in 20nm

Copyright © 2012 Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners Pictures: Micron

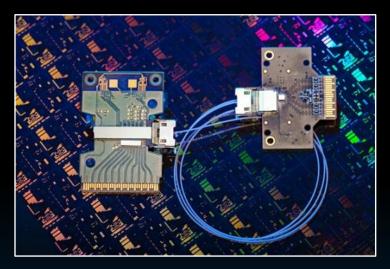

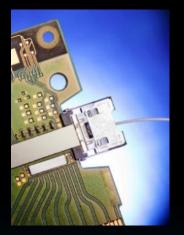

## **Silicon Photonics Research**

### **50Gbps Silicon Photonics Link**

The transmit module (left) sends laser light from the silicon chip at the center of the green board, which then travels through optical fiber to the receiver module (right), where a second silicon chip detects the data on the laser and coverts it back into an electrical signal.

### **Terabits of I/O throughput potential**

Controller chip for conversion from electricity to light and vice versa, using miniature lasers and photo detectors

Chip-to-Chip Board-to-Board System-to-System

Provides substantial size, cost, and power savings over traditional optical communication solutions

## **Silicon Photonics**

### The Path to Tera-scale Data Rates

46

## whatif.intel.com

Access innovations ... in the formative stages

Adobe\* Premiere® Pro/Premiere® Elements Encoder plug-in

New! Intel® Concurrent Collections for C++ Rev 0.7 Released

· New! Intel® Benchmark Install and Test Tool (Intel® BITT) Tools

Intel Advisor Lite Now Part of Intel® Parallel Studio

Smoke - Game Technology Demo Rev 1.2 Released

Intel® Energy Checker SDK Rev 2.0 Release

Intel® SOA Expressway XSLT 2.0 Processor

New! Intel® Cilk Plus Software Development Kit

Intel® Cilk++ Software Development Kit

using Intel® Media SDK and Intel® Quick Sync Video Technology

Communities Partners Tools & Downloads Torums & Support Blog Resources

#### Home , What If Experimental Software What If Experimental Software

What if you could experiment with intel's advanced research and technology inglementations that are still under devicement? And two see your readout advected and the end of the end of the output of the end of the other of the ot collaborate with your peers and send us your feedback through our subsize engineering bogs and supportioning. Pears not built These are the only mechanisms for interactions with vide on bear implementations with Plemer Dopport is on offend to up Control of any end of the set of the other set of the s

#### Active Projects

Designing New Capabilities Adobe\* Premiere® ProiPremiere® Elements Encoder plug-in

- using intel® Media SDK and Intel® Quick Sync Video Technology

- Intel Advisor Lite Now Part of Intel® Parallel Studio

- Intel® Energy Checker SDK Rev 2.8 Release Intel® SDA Expressively XSLT 2.0 Processor Smote - Game Technology Demo Rev 1.2 Released

- Isolated Execution

- Intel® Direct Ethernel Transport Inhel® Software Development Emulator

Creating Concurrent Code

Heref Intel® Concurrent Collections for C++ Rev 0.7 Releases New Intel® Benchmark Install and Test Tool (Mel® BIT) Tools

- New men tencimum analian are real toorent New Intel® City Plus Software Development Kit

- Intel® Cilk++ Software Development Kit

Intel® Adaptive Spine-Based Solver Math Libraries

- Intel® Performance Bottleneck Analyzer 4.0.1 Update Performance Tuning

- Hereased Intel® Software Autobuning Tool New?

- Interity Software Automatig 106

Interity Software Tuning Agent

- Intel® Architecture Code Analytet ing Ubility 4.0 Update 5 Release

Copyright © 2012 Intel Corporation. All rights reserved. \*Other brands and names are the property of their respective owners

Intel® OpenCL SDK - Apha update now available Intel continues to demonstrate its commitment to paratel computing tools and standards su Joint lifetime and access synchronization algorithm for shared Modern programming practices and computer languages (like NET) lend to dynamically create

Expressively oneonly menticel Using a Service Cateway to Protect against the OWASP Top 10 Cramp a centre catenary to motion against the crawber top W The Open Web Application Security Project (OWASP) maintains

What It Support Forums

More

Affoldsupprint 3 to reverse and thorus Affoldsupprint 3 is the latest product by suppl attitude and attitude Voice recognition for faster programming Voice recognition for faster programming Micros Amposer HE Excuse my ignorance tools there a relationship between the

Product Index

- caverines recated to Appria Software wat acclually to a alpha software, how can it be utilized

- Intel® Adaptive Spike-Based Solver Performance Tuning

Math Libraries

Active Projects

New!

Designing New Capabilities

Intel® Web APIs New!

Isolated Execution

Creating Concurrent Code

Intel® Array Building Blocks

Intel® Direct Ethernet Transport

Intel® Software Development Emulator

- Intel® Performance Bottleneck Analyzer 4.0.1 Update Released

- Intel® Software Autotuning Tool New!

- Intel® Software Tuning Agent

- Intel® Architecture Code Analyzer

- Intel® Performance Tuning Utility 4.0 Update 5 Released

- · Intel® Platform Modeling with Machine Learning

#### What If Blogs

Intel® OpenCL SDK - Alpha update now available Intel continues to demonstrate its commitment to parallel

computing tools and standards su...

Joint lifetime and access synchronization algorithm for shared dynamic objects

Modern programming practices and computer languages (like .NET) tend to dynamically create...

Try Intel® SOA Expressway software for yourself ....

Just a guick post to let people know that they can now try SOA Expressway directly themsel...

Using a Service Gateway to Protect against the OWASP Top 10 The Open Web Application Security Project (OWASP) maintains and publishes an oingoing list...

More...

#### What If Support Forums

#### Affiloblueprint 3.0 Review and Bonus

Affiloblueprint 3. is the latest product by super affiliate and affiliate marketing vetera...

Voice recognition for faster programming

Voice recognition for faster programming

#### PTU vs Amplifier

Hi.Excuse my ignorance but is there a relationship between the Performance Tuning Utility

#### Querries related to Alpha software

wat acctually is a alpha software, how can it be utilized

More...

Try Intel® SQA Expressway Software for yourset ing internet course expressioned sourcement yourses. Sust a quick post to let people know that they can now try SOA.

and publishes an oingoing list

### using IEEE 64-bit DP-F.P.

| X <sub>1</sub> | X <sub>2</sub> | X <sub>3</sub> | X <sub>4</sub> | X <sub>5</sub> | $SUM(X_1:X_5)$ |

|----------------|----------------|----------------|----------------|----------------|----------------|

|                |                |                |                |                |                |

|                |                |                |                |                |                |

|                |                |                |                |                |                |

| 1.00E+21       | -1.00E+21      | 17             | -10            | 130            | 137.00         |

| 1.001+21       | -1.00L+21      | 17             | -10            | 130            | 137.00         |

### using IEEE 64-bit DP-F.P.

| X <sub>1</sub> | X <sub>2</sub> | X <sub>3</sub> | X <sub>4</sub> | <b>X</b> <sub>5</sub> | SUM(X <sub>1</sub> :X <sub>5</sub> ) |

|----------------|----------------|----------------|----------------|-----------------------|--------------------------------------|

| 1.00E+21       | 17             | -10            | 130            | -1.00E+21             | 0.00                                 |

|                |                |                |                |                       |                                      |

|                |                |                |                |                       |                                      |

|                |                |                |                |                       |                                      |

| 1.00E+21       | -1.00E+21      | 17             | -10            | 130                   | 137.00                               |

|                |                |                |                |                       |                                      |

### using IEEE 64-bit DP-F.P.

| X1       | X <sub>2</sub> | X <sub>3</sub> | X <sub>4</sub> | <b>X</b> <sub>5</sub> | $SUM(X_1:X_5)$ |

|----------|----------------|----------------|----------------|-----------------------|----------------|

| 1.00E+21 | 17             | -10            | 130            | -1.00E+21             | 0.00           |

|          |                |                |                |                       |                |

|          |                |                |                |                       |                |

| 1.00E+21 | -10            | -1.00E+21      | 130            | 17                    | 147.00         |

| 1.00E+21 | -1.00E+21      | 17             | -10            | 130                   | 137.00         |

|          |                |                |                |                       |                |

### using IEEE 64-bit DP-F.P.

| X <sub>1</sub> | X <sub>2</sub> | X <sub>3</sub> | X <sub>4</sub> | <b>X</b> 5 | $SUM(X_1:X_5)$ |          |

|----------------|----------------|----------------|----------------|------------|----------------|----------|

| 1.00E+21       | 17             | -10            | 130            | -1.00E+21  | 0.00           | ××       |

|                |                |                |                |            |                |          |

|                |                |                |                |            |                |          |

| 1.00E+21       | -10            | -1.00E+21      | 130            | 17         | 147.00         | ×        |

| 1.00E+21       | -1.00E+21      | 17             | -10            | 130        | 137.00         | <b>V</b> |

| 1.00E+21       | 17             | 130            | -1.00E+21      | -10        | -10.00         | XXX      |

using IEEE 64-bit DP-F.P.

| X <sub>1</sub> | X <sub>2</sub> | X <sub>3</sub> | X <sub>4</sub> | X <sub>5</sub> | $SUM(X_1:X_5)$ |          |

|----------------|----------------|----------------|----------------|----------------|----------------|----------|

| 1.00E+21       | 17             | -10            | 130            | -1.00E+21      | 0.00           | ××       |

| 1.00E+21       | -10            | 130            | -1.00E+21      | 17             | 17.00          | ××       |

| 1.00E+21       | 17             | -1.00E+21      | -10            | 130            | 120.00         | ×        |

| 1.00E+21       | -10            | -1.00E+21      | 130            | 17             | 147.00         | ×        |

| 1.00E+21       | -1.00E+21      | 17             | -10            | 130            | 137.00         | <b>V</b> |

| 1.00E+21       | 17             | 130            | -1.00E+21      | -10            | -10.00         | ×××      |

Source: Ulrich Kulisch, Computer Arithmetic and Validity, de Gruyter Studies in Mathematics 33 (2008), p. 250

"Results can be satisfactory, inaccurate or completely wrong. Neither the computation itself nor the computed result indicate which one of the three cases has occurred."

# Thank You.